Закодируйте двоичные выборки с помощью турбо алгоритма

Беспроводной HDL Toolbox/Обнаружение и коррекция ошибок

Блок LTE Turbo Encoder реализует турбо- энкодер, описанную в стандарте LTE TS 36.212 [1], используя интерфейс и архитектуру, оптимизированную для генерации HDL-кода и оборудования развертывания. Энкодер является параллельным сверточным кодом (PCCC) с двумя составляющими энкодерами 8 состояний и внутренним перемежителем. Первый энкодер работает с входным потоком данных, а второй энкодер работает с перемеженной версией входных данных. Блок завершает каждый выход энкодера независимыми хвостовыми битами. Скорость кодирования составляет 1/3. Закодированные выходные биты для каждого входного бита возвращаются как вектор 3 на 1, [S P1 P2]. В этом векторе S - систематический бит, и P1 и P2 являются битами четности от двух энкодеров.

Этот блок использует интерфейс потоковой выборки с шиной для связанных сигналов управления. Этот интерфейс позволяет блоку работать независимо от формата кадра и легко соединяться с другими блоками Toolbox™ Wireless HDL. Блок принимает и возвращает значение, представляющее одну выборку, и шину, содержащую три сигнала управления. Эти сигналы указывают валидность каждой выборки и контуров системы координат. Чтобы преобразовать матрицу в поток сэмплирования и эти сигналы управления, используйте блок Frame To Samples или whdlFramesToSamples функция. Полное описание интерфейса см. в разделе Потоковый пример интерфейса.

Блок может принять новые входные данные после завершения предыдущей системы координат. Примените входные кадры не менее BlockSize + 16 оборотов холостого хода между ними. 16 циклов состоят из 12 циклов для задержек трубопровода в алгоритме и 4 циклов хвостовых бит. Эта задержка не зависит от размера блока. Или можно использовать сигнал выхода ctrl end. чтобы определить, когда блок готов к новому входу.

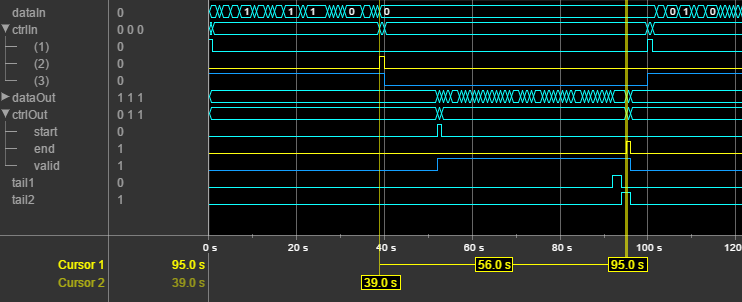

Эта форма волны показывает входной кадр из 40 выборок с 57 циклами простоя между системами координат. Входная и выходная шины ctrl расширены, чтобы показать сигналы управления. start и end показать контуры кадра и valid определяет выборки данных. Необязательные сигналы tail1 и tail2 указывают циклы, когда конечные биты от каждого энкодера действительны.

Вы не можете использовать этот блок внутри Enabled Subsystem или Resettable Subsystem.

[1] 3GPP TS 36.212. «Мультиплексирование и канальное кодирование». 3rd Генерация Partnership Project; Группа технических спецификаций Radio Доступа Network; Evolved Universal Terrestrial Radio Access (E-UTRA). URL-адрес: https://www.3gpp.org.

lteDLSCHInfo (LTE Toolbox) | lteTurboDecode (LTE Toolbox) | lteTurboEncode (LTE Toolbox)