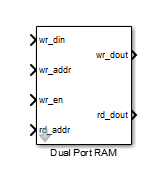

Двухпортовый RAM с двумя выходными портами

HDL Coder / Операции HDL

Блок Dual Port RAM моделирует RAM, который поддерживает одновременные операции чтения и операции записи, и имеет обоих порт вывода данных чтения, и запишите данные выходной порт. Можно использовать этот блок, чтобы сгенерировать HDL-код, который сопоставляет с RAM в большей части FPGAs.

Если вы не должны использовать выходные данные записи, wr_dout, можно достигнуть лучшего вывода RAM с инструментами синтеза при помощи блока Simple Dual Port RAM.

Во время записи новые данные появляются при выводе порта записи (wr_dout) блока Dual Port RAM. Если операция чтения происходит одновременно в том же адресе как операция записи, старые данные появляются в выходном порту чтения (rd_dout).

Ширина адресного бита. Минимальная битная ширина равняется 2, и максимальная битная ширина равняется 29. Значение по умолчанию равняется 8.

Блок имеет следующие порты:

wr_dinЗапишите данные вход. Данные могут быть любой шириной. Это наследовало ширину и тип данных от входного сигнала.

Тип данных: скалярная фиксированная точка, целое число или комплекс

wr_addrЗапишите адрес.

Тип данных: скалярное беззнаковое целое (uintN) или фиксированная точка без знака (ufixN) с дробной длиной 0

wr_enРазрешение записи.

Тип данных: булевская переменная

rd_addrСчитайте адрес.

Тип данных: скалярное беззнаковое целое (uintN) или фиксированная точка без знака (ufixN) с дробной длиной 0

wr_doutВыходные данные от адреса записи, wr_addr.

rd_doutВыходные данные от адреса чтения, rd_addr.

Этот блок имеет одну, архитектуру HDL по умолчанию.

HDL-код, сгенерированный для блоков RAM, имеет:

Задержка одного такта для вывода данных чтения.

Никакой сигнал сброса, потому что некоторые инструменты синтеза не выводят RAM из HDL-кода, если он включает сброс.

Генерация кода для блока RAM создает отдельный файл, blockname.ext. blockname выведен с имени блока RAM. ext является расширением файла выходного языка.

Код, сгенерированный, чтобы инициализировать RAM, предназначается для симуляции только. Инструменты синтеза могут проигнорировать этот код.

Свойство блока HDL, RAMArchitecture, включает или подавляет генерацию часов, включают логику для всех блоков RAM в подсистеме. Можно установить RAMArchitecture на следующие значения:

WithClockEnable (значение по умолчанию): Генерирует RAM с помощью шаблонов HDL, которые включают часы, включают сигнал и пустую обертку RAM.

WithoutClockEnable: Генерирует RAM без часов, включает, и обертка RAM, которая реализует часы, включает логику.

Некоторые инструменты синтеза не выводят RAM с часами, включают. Если ваш инструмент синтеза не поддерживает структуры RAM с часами, включают, и не может сопоставить ваш сгенерированный HDL-код с FPGA ресурсы RAM, установить RAMArchitecture на 'WithoutClockEnable'. Изучить, как сгенерировать RAM без часов, включает для вашего проекта, смотрите Начало работы с примером ROM и RAM. Открыть пример, в командной строке, введите:

hdlcoderramrom

Если вы используете блоки RAM, чтобы выполнить параллельные операции чтения и операции записи, проверьте поведение чтения во время записи в оборудовании. Поведение чтения во время записи RAM блокирует в соответствиях Simulink® тот из сгенерированного поведенческого HDL-кода. Однако, если инструмент синтеза не следует за тем же поведением во время вывода RAM, это заставляет поведение чтения во время записи в оборудовании отличаться от поведения типового кодекса Simulink или сгенерированного HDL-кода.

Ваш инструмент синтеза не может сопоставить сгенерированный код с RAM по следующим причинам:

Небольшой размер RAM: ваш инструмент синтеза использует регистры, чтобы реализовать маленький RAM для лучшей производительности.

Часы включают сигнал, присутствует. Можно подавить генерацию часов, включают сигнал в блоках RAM, как описано в Реализации, которую Включает RAM С или Без Часов.

Количество регистров, чтобы поместить при выходных параметрах путем перемещения существующих задержек в рамках проекта. Распределенная конвейеризация не перераспределяет эти регистры. Значение по умолчанию 0. См. также ConstrainedOutputPipeline.

Количество входных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. Значение по умолчанию 0. См. также InputPipeline.

Количество выходных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. Значение по умолчанию 0. См. также OutputPipeline.

Этот блок поддерживает генерацию кода для комплексных сигналов.

Двойной уровень двухпортовый RAM | Простой двухпортовый RAM | Один порт RAM