Двухпортовый RAM, который поддерживает два уровня

HDL Coder / Операции HDL

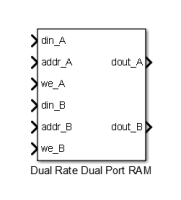

Блок Dual Rate Dual Port RAM моделирует RAM, который поддерживает одновременные операции чтения и операции записи к различным адресам на двух тактовых частотах. Порт RAM может достигнуть одного уровня, и порт B может запуститься на различном уровне.

В высокоэффективных аппаратных приложениях можно использовать этот блок, чтобы получить доступ к RAM дважды на такт. Если вы генерируете HDL-код, это блок-диаграммы к двойному тактовому двухпортовому RAM в большей части FPGAs.

Можно получить доступ к различным адресам от портов A и B одновременно. Можно также считать тот же адрес из портов A и B одновременно.

Однако не получайте доступ к адресу от одного порта RAM, в то время как он пишется из другого порта RAM. Во время симуляции, если вы получаете доступ к адресу от одного порта RAM в то же время, что и вы пишете, что адрес от другого порта RAM, программное обеспечение сообщает об ошибке.

RAM имеет запись первое поведение. То, когда вы пишете в RAM, новые записывают данные, сразу доступно в выходном порту.

Ширина адресного бита. Минимальная битная ширина равняется 2, и максимальная битная ширина равняется 28. Значение по умолчанию равняется 8.

Блок имеет следующие порты:

din_AЗапишите данные вход для порта RAM A. Данные могут быть любой шириной. Это наследовало ширину и тип данных от входного сигнала.

Тип данных: скалярная фиксированная точка, целое число или комплекс

addr_AЗапишите адрес для порта RAM A.

Тип данных: скалярное беззнаковое целое (uintN) или фиксированная точка без знака (ufixN) с дробной длиной 0

we_AРазрешите запись для порта RAM A. Установите we_A на true для операции записи или false для операции чтения.

Тип данных: булевская переменная

din_BЗапишите данные вход для порта RAM B. Данные могут иметь любую ширину и наследовали ширину и тип данных от входного сигнала.

Тип данных: скалярная фиксированная точка, целое число или комплекс

addr_BЗапишите адрес для порта RAM B.

Тип данных: скалярное беззнаковое целое (uintN) или фиксированная точка без знака (ufixN) с дробной длиной 0

we_BРазрешите запись для порта RAM B. Установите we_B на true для операции записи или false для операции чтения.

Тип данных: булевская переменная

dout_AВыходные данные от порта RAM адрес, addr_A.

dout_BВыходные данные от порта RAM B адрес, addr_B.

Для результатов симуляции, которые совпадают со сгенерированным HDL-кодом в панели Решателя диалогового окна Configuration Parameters, снимают флажок для Treat each discrete rate as a separate task. Когда флажок снимается, однозадачный режим включен. Если вы моделируете блок с этим установленным флажком, выходные данные могут обновить в том же цикле, но в сгенерированном HDL-коде, выходные данные обновляются один цикл позже.

Этот блок имеет одну, архитектуру HDL по умолчанию.

HDL-код, сгенерированный для блоков RAM, имеет:

Задержка одного такта для вывода данных чтения.

Никакой сигнал сброса, потому что некоторые инструменты синтеза не выводят RAM из HDL-кода, если он включает сброс.

Генерация кода для блока RAM создает отдельный файл, blockname.ext. blockname выведен с имени блока RAM. ext является расширением файла выходного языка.

Код, сгенерированный, чтобы инициализировать RAM, предназначается для симуляции только. Инструменты синтеза могут проигнорировать этот код.

Свойство блока HDL, RAMArchitecture, включает или подавляет генерацию часов, включают логику для всех блоков RAM в подсистеме. Можно установить RAMArchitecture на следующие значения:

WithClockEnable (значение по умолчанию): Генерирует RAM с помощью шаблонов HDL, которые включают часы, включают сигнал и пустую обертку RAM.

WithoutClockEnable: Генерирует RAM без часов, включает, и обертка RAM, которая реализует часы, включает логику.

Некоторые инструменты синтеза не выводят RAM с часами, включают. Если ваш инструмент синтеза не поддерживает структуры RAM с часами, включают, и не может сопоставить ваш сгенерированный HDL-код с FPGA ресурсы RAM, установить RAMArchitecture на WithoutClockEnable.

Если вы используете блоки RAM, чтобы выполнить параллельные операции чтения и операции записи, проверьте поведение чтения во время записи в оборудовании. Поведение чтения во время записи RAM блокирует в соответствиях Simulink® тот из сгенерированного поведенческого HDL-кода. Однако, если инструмент синтеза не следует за тем же поведением во время вывода RAM, это заставляет поведение чтения во время записи в оборудовании отличаться от поведения типового кодекса Simulink или сгенерированного HDL-кода.

Ваш инструмент синтеза не может сопоставить сгенерированный код с RAM по следующим причинам:

Небольшой размер RAM: ваш инструмент синтеза использует регистры, чтобы реализовать маленький RAM для лучшей производительности.

Часы включают сигнал, присутствует. Можно подавить генерацию часов, включают сигнал в блоках RAM, как описано в Реализации, которую Включает RAM С или Без Часов.

Количество регистров, чтобы поместить при выходных параметрах путем перемещения существующих задержек в рамках проекта. Распределенная конвейеризация не перераспределяет эти регистры. Значение по умолчанию 0. См. также ConstrainedOutputPipeline.

Количество входных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. Значение по умолчанию 0. См. также InputPipeline.

Количество выходных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. Значение по умолчанию 0. См. также OutputPipeline.

Этот блок поддерживает генерацию кода для комплексных сигналов.

Двухпортовый RAM | FIFO HDL | Простой двухпортовый RAM | Один порт RAM