Для проектов, которые требуют больших наборов данных доступа от внешней памяти, смоделируйте свой алгоритм с упрощенным Основным протоколом AXI4. Когда вы запускаете рабочий процесс IP Core Generation, HDL Coder™generates ядро IP с Основными интерфейсами AXI4. Интерфейс AXI4 Master может передать между вашим проектом и контроллером внешней памяти IP при помощи Основного протокола AXI4. Используйте интерфейс AXI4 Master когда ваш:

Разработайте целевые приложения обработки видеоданных сверхкадра. Можно сохранить данные изображения во внешней памяти, такой как память DDR3 на борту, и затем считать или записать изображения в проект пакетным способом для высокоскоростной обработки.

Алгоритм должен получить доступ к данным оперативной памяти в не передающем потоком произвольном шаблоне.

Ядро IP DUT должно управлять другим дюйм/с с ведомым интерфейсом AXI4 в системе. Эта возможность особенно полезна в автономных устройствах FPGA.

Можно использовать упрощенный Основной протокол AXI4, чтобы сопоставить с Основными интерфейсами AXI4. Используйте упрощенный Основной протокол записи AXI4 для транзакции записи и упрощенный Основной протокол чтения AXI4 для транзакции чтения.

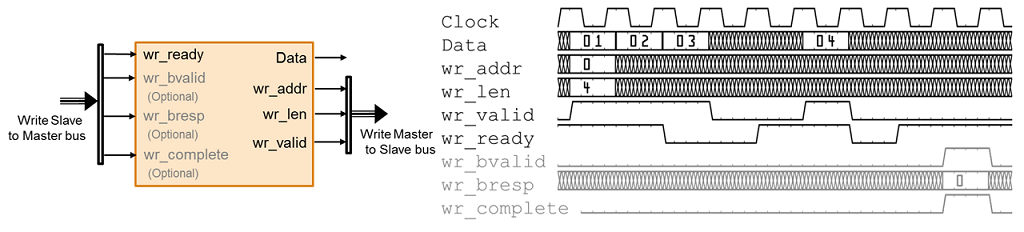

Эти данные показывают схему синхронизации для сигналов, что вы моделируете в интерфейсах ввода и вывода DUT для Основной транзакции записи AXI4.

DUT ожидает wr_ready, чтобы стать высоким, чтобы инициировать запрос записи. Когда wr_ready становится высоким, DUT может отослать запрос записи. Запрос записи состоит из сигналов Write Master to Slave bus и Data. Эта шина состоит из wr_len, wr_addr и wr_valid. wr_addr задает начальный адрес, в который DUT хочет записать. Сигнал wr_len соответствует количеству элементов данных в этой транзакции записи. Data может быть отправлен, пока wr_valid высок. Когда wr_ready становится низким, DUT должен прекратить отправлять данные в одном такте, и сигнал Data становится недопустимым. Если DUT продолжает отправлять данные после того, как один такт, данные будут проигнорированы.

Выходные сигналы

Смоделируйте Data и сигналы Write Master to Slave bus в DUT интерфейс вывода.

Данные: данные, которые вы хотите передать, допустимый каждый цикл транзакции.

Write Master to Slave bus, который состоит из:

wr_addr: Начальный адрес транзакции записи, которая выбирается в первом цикле транзакции.

wr_len: количество значений данных, которые вы хотите передать, выбранный в первом цикле транзакции.

wr_valid: Когда этот управляющий сигнал становится высоким, он указывает, что сигнал Data, выбранный при выводе, допустим.

Входные сигналы

Смоделируйте Write Slave to Master bus, который состоит из:

wr_ready: Этот сигнал соответствует противодавлению от ведомого IP оперативная или внешняя память. Когда этот управляющий сигнал идет высоко, он указывает, что данные могут быть отправлены. Когда wr_ready является низким, DUT должен прекратить отправлять данные в одном такте. Можно также использовать сигнал wr_ready определить, может ли DUT сразу отправить второй пакетный сигнал после того, как первый пакетный сигнал был отправлен. Несколько пакетных сигналов поддерживаются, что означает, что сигнал wr_ready остается высоким, чтобы сразу принять второй пакет после того, как последний элемент первого пакета был принят.

wr_bvalid (дополнительный сигнал): сигнал Ответа от ведомого ядра IP, что можно использовать в целях диагноза. Сигнал wr_bvalid становится высоким после того, как межсоединение AXI4 примет каждую пакетную транзакцию. Если wr_len больше, чем 256, Основной модуль записи AXI4 разделяет большой пакетный сигнал в пакеты 256 размеров. wr_bvalid становится высоким для каждого пакета 256 размеров.

wr_bresp (дополнительный сигнал): сигнал Ответа от ведомого ядра IP, что можно использовать в целях диагноза. Используйте этот сигнал с сигналом wr_bvalid.

wr_complete (дополнительный сигнал): Управляющий сигнал, который, когда остается высоким для одного такта, указывает, что транзакция записи завершилась. Этот сигнал утверждает в последнем wr_bvalid пакета.

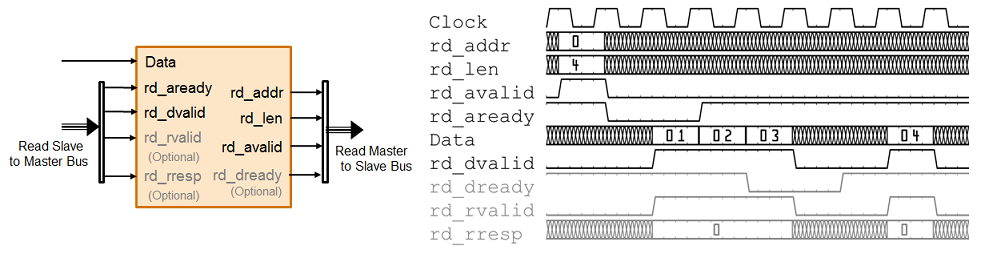

Эти данные показывают схему синхронизации для сигналов, что вы моделируете в интерфейсах ввода и вывода DUT для Основной транзакции чтения AXI4. Эти сигналы включают Data, Read Master to Slave Bus и Read Slave to Master Bus.

DUT ожидает rd_aready, чтобы стать высоким, чтобы инициировать запрос чтения. Когда rd_aready высок, DUT может отослать запрос чтения. Запрос чтения состоит из rd_addr, rd_len и сигналов rd_avalid Read Master to Slave bus. Ведомый IP или внешняя память отвечают на запрос чтения путем отправки Data в каждом такте. Сигнал rd_len соответствует количеству значений данных, чтобы читать. DUT может получить Data, пока rd_dvalid высок.

Считайте запрос

Чтобы смоделировать запрос чтения, в DUT интерфейс вывода, моделируют Read Master to Slave bus, который состоит из:

rd_addr: Начальный адрес для транзакции чтения, которая выбирается в первом цикле транзакции.

rd_len: количество значений данных, которые вы хотите считать, выбранный в первом цикле транзакции.

rd_avalid: Управляющий сигнал, который задает, допустим ли запрос чтения.

В интерфейсе входа DUT реализуйте сигнал rd_aready. Этот сигнал является частью Read Slave to Master bus и указывает, когда принять запросы чтения. Можно контролировать сигнал rd_aready определить, может ли DUT отправить последовательные пакетные запросы. Когда rd_aready становится высоким, он указывает, что DUT может отправить запрос чтения за следующий такт.

Считайте ответ

В интерфейсе входа DUT смоделируйте сигналы Read Slave to Master bus и Data.

Данные: данные, которые возвращены в запрос чтения.

Read Master to Slave bus, который состоит из:

rd_dvalid: Управляющий сигнал, который указывает, что Data, возвращенный в запрос чтения, допустим.

rd_rvalid (дополнительный сигнал): сигнал ответа от ведомого ядра IP, что можно использовать в целях диагноза.

rd_rresp (дополнительный сигнал): сигнал Ответа от ведомого ядра IP, которое указывает на состояние транзакции чтения.

В DUT интерфейс вывода можно опционально реализовать сигнал rd_dready. Этот сигнал является частью Read Master to Slave bus и указывает, когда DUT может начать принимать данные. По умолчанию, если вы не сопоставляете этот сигнал с Ведущим интерфейсом чтения AXI4, сгенерированное ядро IP HDL связывает rd_dready с логикой высоко.

Для ядер IP, которые вы генерируете, HDL Coder включает индексный регистр, чтобы поддержать авторскую разработку драйвера для обоих Основное чтение AXI4 и каналы записи. Индексный регистр добавляется к адресу, который задан портом DUT ADDR, чтобы сформировать Основной адрес AXI4. Эта возможность позволяет драйверу использовать способ адресации, который программирует адрес фиксированного регистра с базовым адресом буфера. Запрограммированный адрес вместе с портом DUT ADDR используется, чтобы индексировать буфер. По умолчанию регистры принимают значение нуля, если вы не используете их.

Можно смоделировать алгоритм с Данными и Основными сигналами протокола AXI4 в портах DUT и затем сопоставить сигналы с Основными интерфейсами AXI4. Чтобы изучить, как смоделировать ваш алгоритм DUT для отображения интерфейса AXI4 Master, откройте эту модель Simulink®. Подсистема DUT содержит простой алгоритм, который считывает данные из DDR и записывает обратно к различному адресу в памяти DDR.

Дважды кликните Подсистему DUT. Модели DDR_Access_Controller Subsystem Основные каналы чтения и записи AXI и имеют Простой Двухпортовый RAM, который вычисляет сигнал wr_data. Если вы дважды кликаете Подсистему DDR_Access_Controller, вы видите два блока Subsystem Обнаружения Ребра, которые генерируют эти два, запускают импульсы как вход к каждому блоку MATLAB function. Модели Edge Detection Subsystem и DDR Read Controller MATLAB Function транзакция чтения. Другие модели Edge Detection Subsystem и DDR Write Controller MATLAB Function транзакция записи. Можно изменить этот проект, чтобы смоделировать только транзакцию записи или транзакцию чтения при помощи одной Подсистемы Обнаружения Ребра и соответствующего блока MATLAB function.

Считайте канал

Контроллер Чтения DDR моделируется как конечный автомат с четырьмя состояниями: INIT, НЕАКТИВНЫЙ, READ_BURST_START и DATA_COUNT. Состояние INIT инициализирует сигналы чтения и входные сигналы RAM. Когда сигнал запуска идет высоко, конечный автомат переключается на Состояние ожидания, и затем ожидает сигнала rd_aready стать высоким. Когда rd_aready становится высоким, переходы конечного автомата к состоянию READ_BURST_START и DUT начинает считывать данные. Конечный автомат затем безусловно переключается на DATA_COUNT, утверждают, и продолжает считывать данные, пока rd_avalid не идет низко.

Запишите канал

Контроллер Записи DDR моделируется подобный каналу Рида как конечный автомат с четырьмя состояниями: НЕАКТИВНЫЙ, WRITE_BURST_START, DATA_COUNT и ACK_WAIT. DUT находится в Состоянии ожидания и затем переключается на состояние WRITE_BURST_START, где это ожидает сигнала wr_ready. Когда wr_ready становится высоким, конечный автомат переключается на DATA_COUNT, утверждают, и начинает записывать данные. Данные допустимы, когда wr_valid высок. DUT продолжает записывать данные, когда wr_ready высок. Когда wr_ready становится низким, конечный автомат переключается на ACK_WAIT, утверждают, и затем ожидает готового сигнала инициировать следующую транзакцию записи.

Чтобы видеть упрощенный Основной протокол AXI4 в действительности, моделируйте модель. Если вам установили DSP System Toolbox™, можно просмотреть и анализировать результаты в Logic Analyzer.

Можно использовать рабочий процесс Генерации Ядра IP, чтобы сгенерировать ядро IP HDL с интерфейсом AXI4 Master. Если вам установили HDL Verifier™, и вы используете плату Xilinx Zynq ZC706, то можно интегрировать ядро IP в Систему По умолчанию с Внешним исходным проектом доступа к памяти DDR3.

Программное обеспечение HDL Coder поддерживает проекты с несколькими частотами дискретизации, когда вы запускаете рабочий процесс Генерации Ядра IP. Когда вы сопоставляете интерфейсные порты с Основными интерфейсами AXI4, чтобы использовать несколько частот дискретизации, гарантировать, что порты DUT, которые сопоставляют с этими интерфейсами AXI4, запущенными на самом быстром уровне проекта после генерации HDL-кода.

Чтобы узнать больше, смотрите Многоскоростную Генерацию Ядра IP.

Можно интегрировать сгенерированное ядро IP HDL с Основными интерфейсами AXI4 в эти исходные проекты HDL Coder:

Default System with External DDR3 Memory Access: Когда вашей целевой платформой является Xilinx Zynq ZC706 evaluation kit.

Default System with External DDR4 Memory Access: Когда вашей целевой платформой является Altera Arria10 SoC development kit.

Чтобы использовать эти исходные проекты, необходимо было установить HDL Verifier™. Эти данные показывают блок-схему высокого уровня архитектуры исходного проекта.

В этой архитектуре блок HDL DUT IP соответствует ядру IP, которое сгенерировано от рабочего процесса IP Core Generation. Другие блоки в архитектуре представляют предопределенный исходный проект, который состоит из основанного на MATLAB® JTAG AXI Master IP, который обеспечивается HDL Verifier. После того, как вы запустите проект FPGA на плате, с помощью JTAG AXI Master IP, можно использовать входные данные в MATLAB, чтобы инициализировать встроенную внешнюю память DDR3. Ядро HDL DUT IP читает входные данные из внешней памяти через интерфейс AXI4 Master. Ядро IP затем выполняет вычисление алгоритма и пишет результат в память DDR3 через интерфейс AXI4 Master. JTAG AXI Master IP может считать результат памяти DDR3 и затем проверить результат в MATLAB.

Используя метод addAXI4MasterInterface класса hdlcoder.ReferenceDesign, можно интегрировать ядро IP с Основным Интерфейсом AXI4 в собственный исходный проект.

Synthesis tool: Должен быть Xilinx Vivado или Altera QUARTUS II. Xilinx ISE не поддержан.

Target workflow: Используйте рабочий процесс IP Core Generation. Чтобы запустить рабочий процесс, откройте HDL Workflow Advisor из своего алгоритма DUT в Simulink®. MATLAB к рабочему процессу HDL не поддержан.

Processor/FPGA synchronization: Должен быть режим Free running.

Поддержка типов данных: Для порта Data используйте скалярные типы данных. Векторные типы данных не поддержаны.