Чтобы выполнить легкую передачу данных или к регистрам управления доступом, используйте ведомые интерфейсы AXI4. Ведомые интерфейсы AXI4 включают AXI4 и AXI4-облегченные интерфейсы. С программным обеспечением HDL Coder™ вы не должны реализовывать AXI4 или AXI4-облегченный протокол в вашей модели. Программное обеспечение генерирует AXI4 или AXI4-облегченные интерфейсы в ядре IP HDL.

Когда вы моделируете свой проект, задаете порты данных, которые вы хотите сопоставить с ведомыми интерфейсами AXI4. HDL Coder затем сопоставляет порты данных с ведомым устройством AXI4 с отображенной памятью, соединяет интерфейсом и выделяет смещения адреса для портов.

Когда вы сопоставляете свои порты DUT с AXI4 или AXI4-облегченными интерфейсами:

Можно сопоставить все скалярные или векторные порты в проекте или к AXI4 или к AXI4-облегченным интерфейсам. Вы не можете сопоставить некоторые порты DUT с интерфейсами AXI4 и другие порты DUT к AXI4-облегченным интерфейсам для того же проекта.

Можно использовать односкоростной проект или проект с несколькими частотами дискретизации без каких-либо ограничений при отображении портов DUT с ведомыми интерфейсами AXI4 при помощи режима синхронизации Free Running для Processor/FPGA Synchronization.

Можно использовать режим Coprocessing-Blocking для Processor/FPGA Synchronization при отображении с AXI4 или AXI-облегченными интерфейсами. Другие интерфейсные типы, такие как AXI4-поток и Ведущее устройство AXI4 не поддерживают этот режим. См. также Синхронизация FPGA и Процессор.

Когда вы используете скалярные типы данных в интерфейсных портах DUT, можно сопоставить интерфейсные порты непосредственно с AXI4 или AXI4-облегченными интерфейсами. Генератор кода присваивает уникальный адрес каждому порту данных, который вы хотите сопоставить с интерфейсом AXI4.

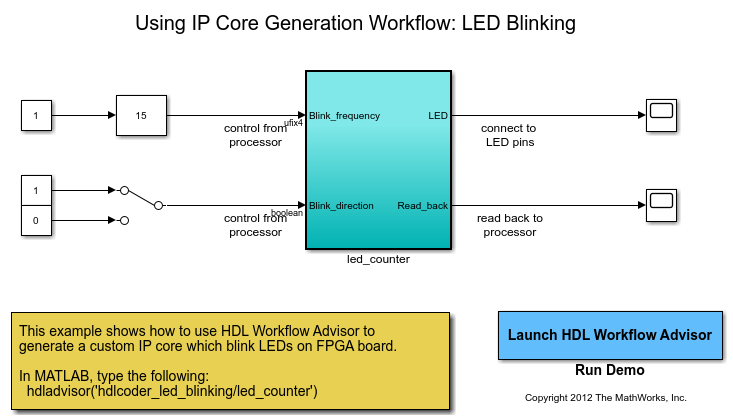

Для примера, который показывает, как сопоставить скалярные порты с AXI4-облегченными интерфейсами, открыть модель hdlcoder_led_blinking.

open_system('hdlcoder_led_blinking')

В этой модели подсистема led_counter является аппаратной подсистемой. Это моделирует счетчик, который мигает светодиодами на плате FPGA. Два входных порта, Blink_frequency и Blink_direction, являются портами управления, которые определяют частоту мигания LED и направление. Все блоки за пределами подсистемы led_counter для реализации программного обеспечения.

В Simulink® можно использовать блок Slider Gain или Ручной блок switch, чтобы настроить входные значения аппаратной подсистемы. Во встроенном программном обеспечении это означает, что процессор ARM управляет сгенерированным ядром IP путем записи в интерфейс AXI доступных регистров. Выходной порт аппаратной подсистемы соединяется с оборудованием LED. Можно использовать выходной порт Read_back, чтобы считать данные назад в процессор.

Когда вы запускаете рабочий процесс IP Core Generation в задаче Set Target Interface, вы видите, что порты Blink_frequency, Blink_direction и Read_back сопоставляют с AXI4-облегченными интерфейсами.

Чтобы узнать больше об этом примере, см.:

Когда вы используете векторные типы данных в интерфейсных портах DUT, можно сопоставить интерфейсные порты непосредственно с AXI4 или AXI4-облегченными интерфейсами. Генератор кода присваивает уникальный адрес для каждого порта данных, который вы хотите сопоставить с интерфейсом AXI4.

Когда вы сопоставляете векторные порты, HDL Coder использует дополнительные регистры строба для каждого порта, чтобы поддержать синхронизацию с логикой основного алгоритма IP. Для входных портов регистры строба управляют разрешать сигналами для набора теневых регистров, который заставляет логику основного алгоритма IP видеть обновленные векторные элементы одновременно. Для выходных портов регистры строба убеждаются, что векторные данные, которые будут считаны, собраны синхронно.

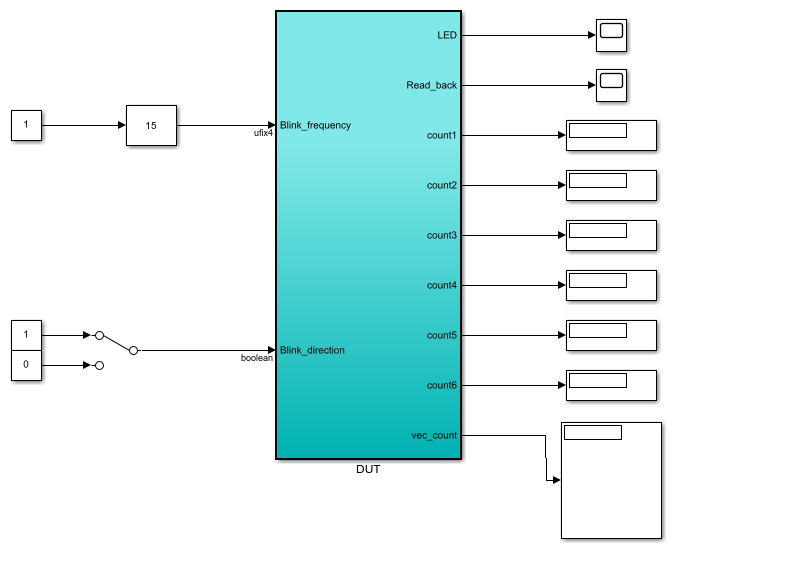

Для примера, который показывает, как сопоставить векторные порты с AXI4-облегченными интерфейсами, открыть модель hdlcoder_led_vector.

open_system('hdlcoder_led_vector')

В этой модели подсистема DUT реализует LED мигающий алгоритм и имеет векторные выходные порты. Когда вы запускаете рабочий процесс IP Core Generation в задаче Set Target Interface, вы видите, что входные порты и выходные порты сопоставляют с AXI4-облегченными интерфейсами.

Чтобы узнать больше, смотрите Рабочий процесс Генерации Ядра IP с процессором MicroBlaze: Xilinx Kintex-7 KC705.

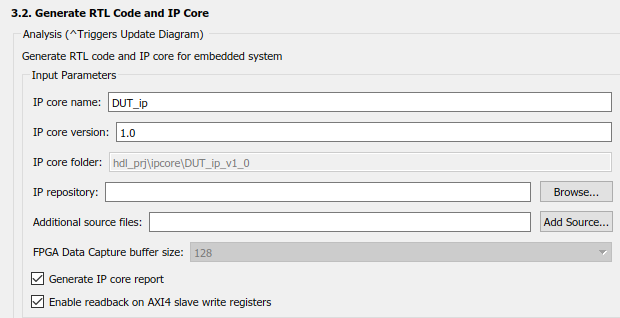

Когда вы запускаете рабочий процесс IP Core Generation, можно считать назад значение, которое записано в ведомые регистры AXI4 при помощи ведомого интерфейса AXI4. Например, можно считать назад значения, которые записаны в ведомые регистры AXI4 при помощи команды devmem в консоли Linux процессора ARM. Если вам установили HDL Verifier™, можно использовать MATLAB в качестве Ведущего IP AXI, чтобы считать назад значения.

Чтобы использовать эту возможность, в задаче Generate RTL Code and IP Core рабочего процесса IP Core Generation, устанавливают флажок Enable read back on AXI4 slave write registers, и затем запускают эту задачу.

Когда вы запускаете эту задачу, HDL Coder сохраняет чтение назад настройка, которую вы включили на модели. В HDL Block Properties Подсистемы DUT, на разделе IP Core Parameter вкладки Target Specification, вы видите параметр набор AXI4RegisterReadback к on. Если вы экспортируете HDL Workflow Advisor, запущенный в скрипт, вы видите, что эта установка экономила на модели при помощи hdlset_param.

hdlset_param('hdlcoder_led_vector/DUT', 'AXI4RegisterReadback', 'on');

Когда вы включаете чтение назад на ведомых регистрах AXI4, HDL Coder добавляет мультиплексор для каждого регистра AXI4 в логике Дешифратора адреса, чтобы сравнить адрес, что данные записаны в при чтении значений. Когда вы читаете значения из нескольких ведомых регистров AXI4, чтение назад логика может стать длинной цепочкой мультиплексора, которая может влиять на частоту синтеза.

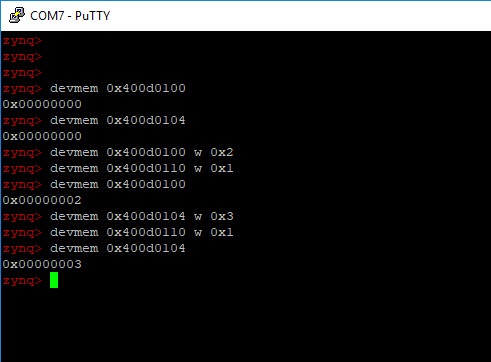

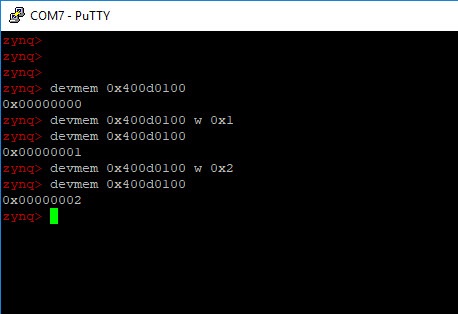

Эти примеры показывают, как можно считать назад значения при помощи команды devmem в консоли Linux с программой, такие как PuTTy™.

Чтобы считать назад значения при отображении скалярных портов с интерфейсами AXI4, вы сначала пишете значения в регистры AXI4, и затем читаете назад значения. Вы видите адрес памяти регистров AXI4 в отчете Генерации Ядра IP.

Чтобы считать назад значения при отображении векторных портов с интерфейсами AXI4, вы сначала пишете в регистры AXI4, затем пишете адрес регистра строба с 0x1, и затем читаете назад значения. Вы видите адрес памяти регистров AXI4 и регистра строба в отчете Генерации Ядра IP.