В этом примере показано, как создать тестовый стенд HDL и проверить созданный код для простой модели счетчика. Чтобы создать код HDL для этой модели, см. раздел Создание кода HDL из модели Simulink. Если код HDL для этой модели не создан, HDL Coder™ запускает генерацию кода перед созданием средства тестирования.

Для проверки функциональности кода HDL для DUT создайте тестовый стенд HDL. Испытательный стенд включает в себя:

Данные стимула, генерируемые источниками сигнала, подключенными к тестируемому объекту.

Выходные данные, сгенерированные тестируемым объектом. Во время испытательного стенда эти данные сравниваются с выходами модели VHDL ® для проверки.

Входы синхронизации, сброса и синхронизации активизируются для управления тестируемым объектом.

Экземпляр компонента тестируемого объекта.

Код для управления тестируемым объектом и сравнения его выходных данных с ожидаемыми данными.

Можно смоделировать созданный тестовый стенд и файлы сценариев с помощью симулятора Mentor Graphics ® ModelSim ®.

Откройте эту модель, чтобы увидеть простой счетчик. Модель подсчитывается от нуля до порогового значения, а затем возвращается к нулю. Пороговое значение устанавливается равным 15. Чтобы изменить пороговое значение, измените значение ввода на count_threshold порт. Сигнал Enable указывает, имеет ли счетчик предыдущее значение. Значение 1 указывает, что счетчик постоянно подсчитывается вверх.

Если установлен Verifier™ HDL, можно также проверить созданный код HDL с помощью этих методов.

| Метод проверки | Для получения дополнительной информации |

|---|---|

| Косимуляция ЛПВП | Cosimulation |

| Испытательный стенд SystemVerilog DPI | Испытательный стенд SystemVerilog DPI |

| FPGA-в-контуре | FPGA-в-контуре |

Создайте код испытательного стенда VHDL или Verilog. По умолчанию код HDL и код тестового стенда записываются в одну и ту же целевую папку. hdlsrc относительно текущей папки.

Для модели счетчика HDL_DUT подсистема является DUT. Чтобы создать средство тестирования, выберите эту подсистему.

На вкладке Приложения выберите Кодер HDL.

Выберите подсистему DUT, HDL_DUTи убедитесь, что это имя отображается в параметре «Код для» на вкладке «Код HDL». Чтобы запомнить выбор, закрепите этот параметр. Щелкните Генерировать тестовые инструменты (Generate Testbench).

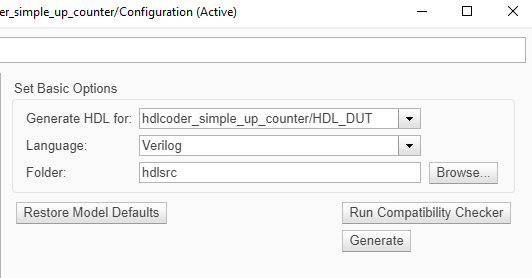

Чтобы создать код тестового средства Verilog для модели счетчика:

На вкладке Код HDL (HDL Code) щелкните Настройки (Settings).

На панели «Создание кода HDL» в поле «Язык» выберите Verilog.

На панели «Создание кода HDL» > «Испытательный стенд» щелкните «Создать испытательный стенд».

Кодер HDL компилирует модель и генерирует тестовый стенд.

Создание тестового стенда завершено и выводит это сообщение. Созданные файлы отображаются в hdlsrc папка.

### HDL TestBench Generation Complete.

Для модели счетчика hdlsrc содержит эти файлы тестового стенда.

HDL_DUT_tb.vhdКод испытательного стенда VHDL, содержащий сгенерированные тестовые и выходные данные. При создании кода тестового стенда Verilog создается файл HDL_DUT_tb.v.

HDL_DUT_tb_pkg.vhdФайл пакета для кода испытательного стенда VHDL. Этот файл не создается, если в качестве целевого языка указан Verilog.

HDL_DUT_tb_compile.do: Сценарий компиляции Mentor Graphics ModelSim (vcom команды). Этот сценарий компилирует и загружает тестируемую сущность (HDL_DUT.vhd) и код испытательного стенда (HDL_DUT_tb.vhd).

HDL_DUT_tb_sim.do: Mentor Graphics ModelSim скрипт для инициализации симулятора, настройки отображения сигнала волнового окна и запуска моделирования.

Для просмотра созданного кода тестового стенда в редакторе MATLAB ® дважды щелкните значокHDL_DUT_tb.vhd или HDL_DUT_tb.v в текущей папке.

Для проверки результатов моделирования можно использовать симулятор Mentor Graphics ModelSim. Необходимо установить Mentor Graphics ModelSim.

Чтобы открыть симулятор, используйте vsim (Проверка HDL). Эта команда показывает, как открыть симулятор, указав путь к исполняемому файлу:

vsim('vsimdir','C:\Program Files\ModelSim\questasim\10.6b\win64\vsim.exe')

Для компиляции и выполнения моделирования сгенерированной модели и кода тестового стенда используйте сгенерированные скрипты кодера HDL. Для модели счетчика выполните эти команды для компиляции и моделирования созданного тестового стенда для HDL_DUT Подсистема.

Откройте программное обеспечение Mentor Graphics ModelSim и перейдите в папку, содержащую созданные файлы кода и сценарии.

Созданный сценарий компиляции используется для компиляции и загрузки созданной модели и текстового кода стенда. Для HDL_DUT выполните эту команду для компиляции сгенерированного кода.

QuestaSim>do HDL_DUT_tb_compile.do

Для выполнения моделирования используйте созданный сценарий моделирования. В следующем списке отображается команда. Можно игнорировать предупреждающие сообщения. Для HDL_DUT Subsystem, выполните эту команду для моделирования сгенерированного кода.

QuestaSim>do HDL_DUT_tb_sim.do

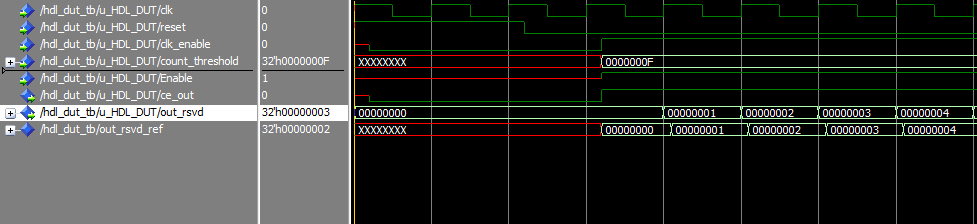

Симулятор оптимизирует конструкцию и отображает результаты в окне волны. если результаты моделирования не отображаются, откройте окно волны. Сценарий моделирования отображает входы и выходы в модели, включая сигналы синхронизации, сброса и включения синхронизации в окне волны.

Теперь можно просмотреть сигналы и убедиться, что результаты моделирования соответствуют функциям исходной конструкции. После проверки закройте симулятор Mentor Graphics ModelSim, а затем закройте открытые файлы в редакторе MATLAB.

Чтобы развернуть созданный код на целевом устройстве FPGA, используйте Simulink ® HDL Workflow Advisor. См. раздел Генерация кода HDL и синтез FPGA от Simulink Model.