Для облегченной передачи данных или доступа к регистрам управления следует использовать AXI4 подчиненные интерфейсы. Ведомые интерфейсы AXI4 включают в себя интерфейсы AXI4 и AXI4-Lite. В программном обеспечении HDL Coder™ нет необходимости внедрять в модель протокол AXI4 или AXI4-Lite. Программное обеспечение генерирует AXI4 или AXI4-Lite интерфейсы в ядре IP HDL.

При моделировании конструкции укажите порты данных, которые необходимо сопоставить с AXI4 подчиненными интерфейсами. Затем кодер HDL сопоставляет порты данных с реестрами, отображаемыми в памяти, и распределяет смещения адресов для портов.

При сопоставлении портов DUT с AXI4 или AXI4-Lite интерфейсами:

Можно сопоставить все скалярные, векторные или шинные порты в конструкции с AXI4 или AXI4-Lite интерфейсами.

Нельзя сопоставить некоторые порты DUT с AXI4 интерфейсами, а другие порты DUT - с AXI4-Lite интерфейсами для той же конструкции.

При использовании скалярных типов данных в интерфейсных портах DUT можно напрямую сопоставить интерфейсные порты с AXI4 или AXI4-Lite интерфейсами. Генератор кода назначает уникальный адрес каждому порту данных, который требуется сопоставить с интерфейсом AXI4.

Для примера, показывающего, как сопоставить скалярные порты с AXI4-Lite интерфейсами, откройте модель. hdlcoder_led_blinking.

open_system('hdlcoder_led_blinking')

В этой модели подсистема led_counter является подсистемой аппаратных средств. Он моделирует счетчик, мигающий светодиодными индикаторами на плате FPGA. Два входных порта, Blink_frequency и Blink_direction, являются управляющими портами, которые определяют частоту и направление мигания светодиода. Все блоки вне подсистемы led_counter предназначены для реализации программного обеспечения.

В Simulink ® можно использовать блок усиления ползунка или блок ручного переключения для настройки входных значений аппаратной подсистемы. Процессор ARM управляет сформированным ядром IP путем записи в регистры интерфейса AXI, доступные во встроенном ПО. Порт вывода подсистемы аппаратных средств подключается к аппаратным средствам светодиодных индикаторов. Можно использовать порт выводаRead_back для считывания данных обратно в процессор.

При запуске IP Core Generation workflow-процесс в задаче Set Target Interface показывает, что порты Blink_frequency, Blink_direction, и Read_back сопоставить с AXI4-Lite интерфейсами.

Дополнительные сведения об этом примере см. в следующих разделах:

При использовании векторных типов данных в интерфейсных портах DUT можно напрямую сопоставить интерфейсные порты с AXI4 или AXI4-Lite интерфейсами. Генератор кода назначает уникальный адрес для каждого порта данных, который требуется сопоставить с интерфейсом AXI4.

При отображении векторных портов кодер HDL использует дополнительные стробные регистры для каждого порта для поддержания синхронизации с логикой алгоритма ядра IP. Для входных портов стробные регистры управляют разрешающими сигналами для набора теневых регистров, заставляя логику алгоритма IP-ядра одновременно видеть обновленные векторные элементы. Для выходных портов стробовые регистры обеспечивают синхронный захват считываемых векторных данных.

Для примера, показывающего, как сопоставить векторные порты с AXI4-Lite интерфейсами, откройте модель. hdlcoder_led_vector.

open_system('hdlcoder_led_vector')

В этой модели подсистема DUT реализует алгоритм мигания светодиода и имеет векторные выходные порты. При запуске IP Core Generation рабочий процесс показывает, что входные порты и выходные порты сопоставляются с AXI4-Lite интерфейсами в задаче Set Target Interface.

Дополнительные сведения см. в разделе Рабочий процесс поколения IP Core с процессором MicroBlaze: Xilinx Kintex-7 KC705.

При использовании типов данных шины в интерфейсных портах DUT можно напрямую сопоставить интерфейсные порты с AXI4 или AXI4-Lite интерфейсами.

При сопоставлении типов данных шины кодер HDL назначает уникальный адрес для каждого порта данных, который требуется сопоставить с интерфейсом AXI4. Шины верхнего и нижнего уровня не имеют адреса смещения регистра. Сопоставление адресов для отдельных скалярных или векторных элементов шины не является смежным.

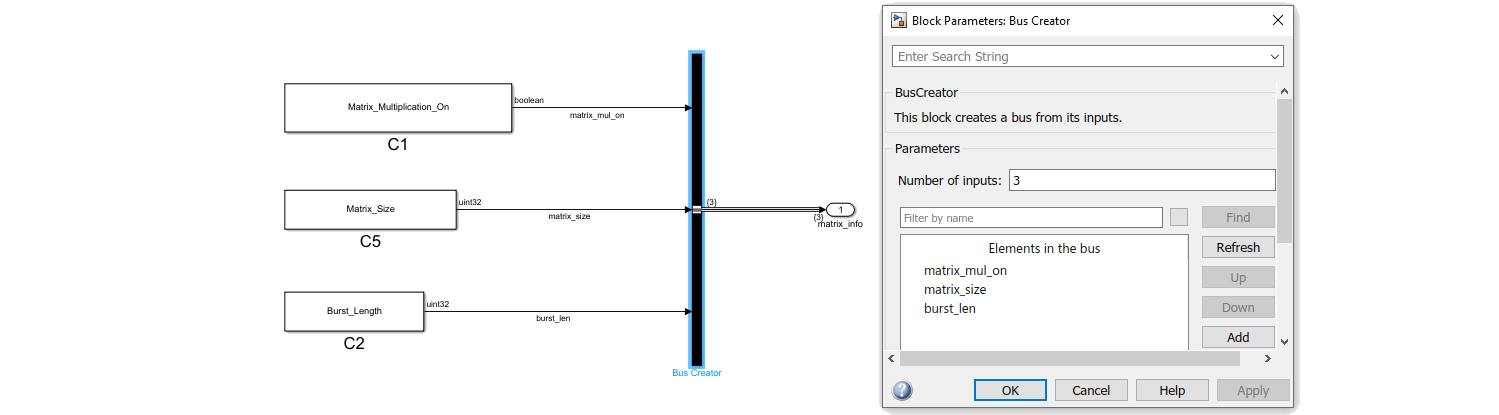

Моделирование элемента шины с использованием блока создания шины или блока элементов шины для создания порта шины.

Моделирование элемента шины с помощью блока создания шины.

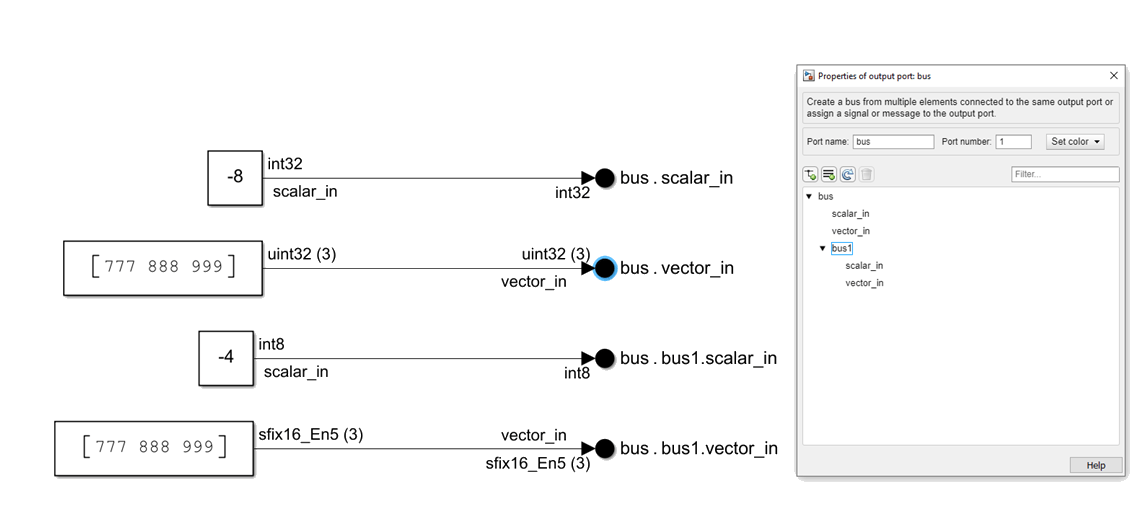

Моделирование элемента шины с использованием блоков элементов шины:

Дополнительные сведения см. в разделе Сопоставление типов данных шины с AXI4 подчиненными интерфейсами.

При запуске IP Core Generation рабочий процесс или Simulink Real-Time FPGA I/O , можно указать начальное значение для входных портов, сопоставленных с AXI4 подчиненными регистрами. Можно указать начальное значение при сопоставлении с этими целевыми интерфейсами:

AXI4

AXI4-Lite

PCIe

По умолчанию начальное значение равно нулю. Чтобы задать ненулевое значение, выполните следующие действия.

В таблице интерфейса целевой платформы при сопоставлении входного порта DUT с AXI4 подчиненным интерфейсом в столбце «Параметры интерфейса» появляется кнопка «Параметры».

Нажмите кнопку Параметры и укажите значение RegisterInitityValue.

Указанное значение сохраняется в блоках DUT Inport как свойство блока HDL IOInterfaceOptions на вкладке Целевая спецификация. Например, если входной порт DUT сопоставлен AXI4-Lite интерфейсу, установите значение RegisterInitityValue равным 5, а затем запустите задачу Set Target Interface. Свойство IOInterateOptions этого входного порта сохраняется со значением{'RegisterInitialValue','5'}.

Для просмотра IOInterfaceOptions значение, если полный путь к порту DUT hdlcoder_led_blinking/led_counter/LED, введите:

hdlget_param('hdlcoder_led_blinking/led_counter/LED',... 'IOInterfaceOptions')

Укажите начальное значение для скалярных портов.

hdlset_param('hdlcoder_led_blinking/led_counter/LED', ... 'IOInterfaceOptions', {'RegisterInitialValue','5'});

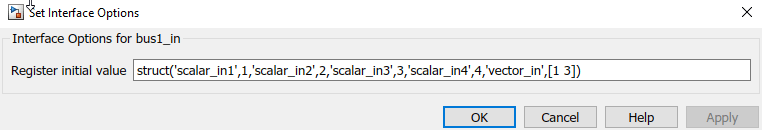

Чтобы задать начальное значение для шины, укажите структуру, имена полей которой соответствуют именам элементов шины. Например,

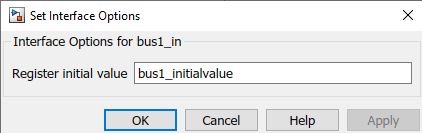

Можно также указать начальное значение с помощью переменной, определенной в рабочей области MATLAB ®. Например:

bus1_initialvalue = struct('scalar_in1',1,'scalar_in2',2,'scalar_in3',3,'scalar_in4',4,'vector_in',[1 3])

При запуске IP Core Generation технологический процесс, Вы можете прочитать назад стоимость, которая написана спискам рабов AXI4 при помощи рабского интерфейса AXI4. Например, можно считывать значения, записанные в AXI4 подчиненные регистры с помощью devmem в консоли Linux процессора ARM. Если установлен HDL Verifier™, для считывания значений можно использовать MATLAB в качестве AXI Master IP.

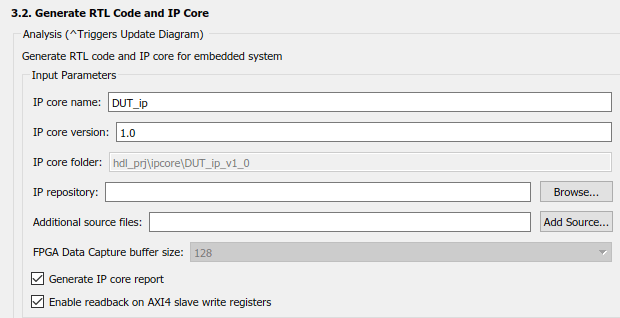

Для использования этой возможности в задаче Generate RTL Code and IP Core IP Core Generation workflow-процесс, установите флажок Enable read back on AXI4 slave write regisers, а затем запустите задачу Generate RTL Code and IP Core

При выполнении этой задачи кодер HDL сохраняет настройку обратного чтения, включенную в модели. В разделе IP Core Parameter вкладки Target Specification (Целевая спецификация) раздела Свойства блока HDL подсистемы DUT (HDL Block Properties of the DUT Subsystem) отображается параметр, для AXI4RegisterReadback установлено значение on. При экспорте запуска помощника по рабочим процессам HDL в сценарий эта настройка сохраняется в модели с помощью hdlset_param.

hdlset_param('hdlcoder_led_vector/DUT', 'AXI4RegisterReadback', 'on');

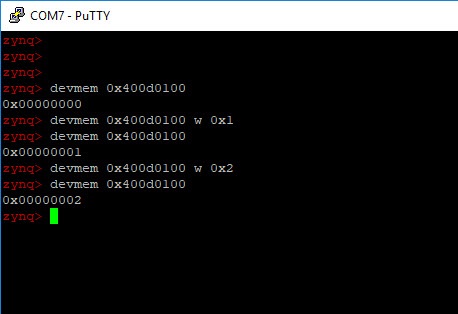

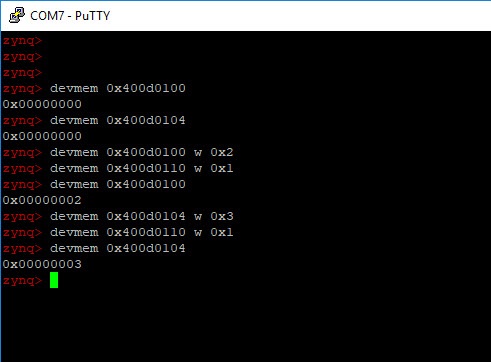

В этих примерах показано, как можно считывать значения с помощью devmem в консоли Linux с такой программой, как PuTTy™.

Для считывания значений при сопоставлении скалярных портов с AXI4 интерфейсами сначала необходимо записать значения в регистры AXI4, а затем прочитать значения. Адрес памяти регистров AXI4 можно просмотреть в отчете по генерации IP Core.

Для считывания значений при сопоставлении векторных портов с AXI4 интерфейсами сначала необходимо записать в AXI4 регистры, а затем записать адрес стробного регистра с помощью 0x1, а затем прочитайте значения. Адрес памяти регистров AXI4 и регистра строба можно просмотреть в отчете о генерации IP Core.

Когда модель содержит несколько выходных регистров и требуется считывать данные из нескольких AXI4 подчиненных регистров, логика считывания становится длинной мультиплексорной цепью, которая может уменьшить частоту синтеза. При выборе параметра Enable readback on AXI4 slave write regisers в задаче Generate RTL Code and IP Core, кодер HDL добавляет мультиплексор для каждого регистра AXI4 в логике декодера адресов. По мере увеличения числа AXI4 подчиненных регистров мультиплексорная цепь становится длиннее, что дополнительно снижает частоту синтеза.

Можно оптимизировать логику обратного чтения и достичь нужной целевой частоты. При запуске IP Core Generation технологический процесс, в Генерировании Кода RTL и IP Основной задачи, Вы видите настройку ведомый порт AX4 к отношению регистра трубопровода. Значение по умолчанию для этого параметра: auto. Этот параметр указывает AXI4 сколько ведомых регистров вставлено в конвейерный регистр. Например, AX4 отношение ведомого порта к регистру трубопровода 20 означает, что один регистр трубопровода вставляется для каждого 20 Ведомый регистр AXI. auto установка означает, что генератор кода вставляет определенное количество конвейеров для подчиненных портов AXI4 в зависимости от количества портов и указанного средства синтеза. Можно отключить этот параметр или выбрать число между 5 и 50 для этого соотношения.

При выполнении этой задачи кодер HDL сохраняет значение, указанное для настройки в модели. В HDL Block Properties Подсистемы DUT, на разделе IP Core Parameter вкладки Target Specification, Вы видите параметр набор AX4SlavePortToPipelineRegisterRatio к стоимости, которую Вы определили. При экспорте запуска помощника по рабочим процессам HDL в сценарий эта настройка сохраняется в модели с помощью hdlset_param.

hdlset_param('hdlcoder_led_vector/DUT', ... 'AXI4SlavePortToPipelineRegisterRatio', '20');