В этом примере показано, как создать стенд для тестирования HDL и проверить созданный код для проекта. В примере предполагается, что для модели создан код HDL. Если код HDL не создан, можно открыть эту модель и создать тестовый стенд HDL. Перед созданием тестового стенда ЛПВП Coder™ запускает генерацию кода, чтобы убедиться в наличии по крайней мере одного успешного запуска генерации кода перед генерацией тестового инструментария.

В этом примере показано, как проверить созданный код для модели фильтра FIR. Сведения о создании кода HDL для этой модели см. в разделе Создание кода HDL из модели Simulink с использованием параметров конфигурации.

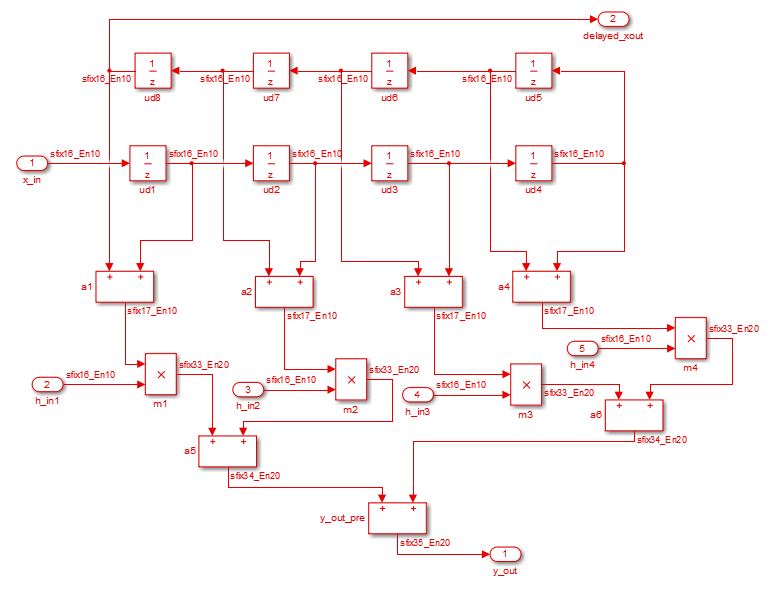

В этом примере используется модель симметричного фильтра FIR, совместимая с генерацией кода HDL. Чтобы открыть эту модель в командной строке, введите:

sfir_fixed

Модель использует разделение труда, которое подходит для конструирования ЛПВП.

symmetric_fir подсистема, реализующая алгоритм фильтрации, является тестируемым устройством (DUT). Объект HDL генерируется из этой подсистемы.

Компоненты модели верхнего уровня, управляющие подсистемой, работают как испытательный стенд.

Модель верхнего уровня генерирует 16-разрядные входные сигналы с фиксированной точкой для symmetric_fir подсистема. Блок «Сигнал из рабочего пространства» генерирует тестовый входной (стимулирующий) сигнал для фильтра. Четыре постоянных блока обеспечивают коэффициенты фильтра. Блоки Scope используются для моделирования и не используются для генерации кода HDL.

Для перехода к symmetric_fir подсистема, введите:

open_system('sfir_fixed/symmetric_fir')

В MATLAB ®:

Создание папки с именем sl_hdlcoder_work, например:

mkdir C:\work\sl_hdlcoder_work

sl_hdlcoder_work хранит локальную копию модели примера и папок и сгенерированный код HDL. Используйте папку, которая не находится в дереве папок MATLAB.

Сделать sl_hdlcoder_work папка рабочая папка, например:

cd C:\work\sl_hdlcoder_workСохранение локальной копии sfir_fixed в текущую рабочую папку. Оставьте модель открытой.

Для проверки функциональных возможностей кода HDL, созданного для DUT, создайте тестовый стенд HDL. Испытательный стенд включает в себя:

Данные стимула, генерируемые источниками сигнала, подключенными к тестируемому объекту.

Выходные данные, сгенерированные тестируемым объектом. Во время испытательного стенда эти данные сравниваются с выходными данными кода VHDL ® для целей проверки.

Входы синхронизации, сброса и синхронизации активизируются для управления тестируемым объектом.

Экземпляр компонента тестируемого объекта.

Код для управления тестируемым объектом и сравнения его выходных данных с ожидаемыми данными.

Созданный тестовый стенд и файлы сценариев можно смоделировать с помощью симулятора Mentor Graphics ® ModelSim ®.

В этом примере показано, как создать стенд для тестирования ЛПВП для моделирования и проверки созданного кода ЛПВП для проекта. Можно также проверить созданный код HDL из модели, используя следующие методы:

| Метод проверки | Для получения дополнительной информации |

|---|---|

| Модель проверки | Сгенерированная модель и модель проверки |

| Косимуляция ЛПВП (требует Verifier™ ЛПВП) | Cosimulation |

| Тестовый стенд SystemVerilog DPI (требует проверки HDL) | Испытательный стенд SystemVerilog DPI |

| FPGA-in-the-Loop (требуется верификатор HDL) | FPGA-в-контуре |

В зависимости от того, был ли создан код VHDL или Verilog, создайте код стенда VHDL или Verilog. Код тестового стенда управляет кодом HDL, сгенерированным для DUT. По умолчанию код HDL и код тестового стенда записываются в одну и ту же целевую папку. hdlsrc относительно текущей папки.

Для фильтра FIR подсистемой symmetric_fir является DUT. Чтобы создать средство тестирования, выберите эту подсистему. Невозможно создать тестовый инструментарий HDL для всей модели.

На вкладке Приложения выберите Кодер HDL. Появится вкладка Код HDL (HDL Code).

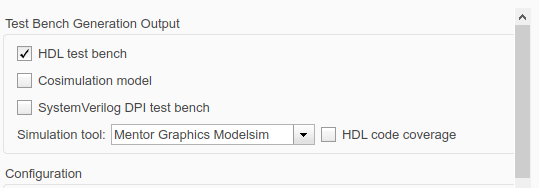

Выберите подсистему DUT в модели и убедитесь, что это имя подсистемы отображается в параметре Code for. Чтобы запомнить выбор, можно закрепить этот параметр. Щелкните Генерировать тестовые инструменты (Generate Testbench).

По умолчанию кодер HDL генерирует код тестовых средств VHDL в целевом объекте hdlsrc папка.

Если требуется создать код тестового стенда Verilog, можно указать этот параметр на панели Создание кода HDL (HDL Code Generation) диалогового окна Параметры конфигурации (Configuration Parameters).

Чтобы создать код тестового средства Verilog для модели счетчика:

На вкладке Код HDL (HDL Code) щелкните Настройки (Settings).

На панели «Создание кода HDL» в поле «Язык» выберите Verilog. Оставьте другие параметры по умолчанию.

В меню «Создание кода HDL» > «Тест-тест» выберите «Создать тестовый стенд».

Если код для модели еще не создан, кодер HDL компилирует модель и генерирует код HDL перед созданием тестового стенда. В зависимости от опций отображения модели, таких как типы данных портов, модель может изменяться в виде после генерации кода.

По мере формирования тестового стенда кодер HDL отображает сообщения о ходе выполнения. Процесс должен завершиться сообщением

### HDL TestBench Generation Complete.

После создания тестового стенда созданные файлы отображаются в hdlsrc папка.

symmetric_fir_tb.vhdКод испытательного стенда VHDL с сгенерированными тестовыми и выходными данными. При создании кода тестового стенда Verilog создается файл symmetric_fir_tb.v.

symmetric_fir_tb_pkg.vhdФайл пакета для кода испытательного стенда VHDL. Этот файл не создается, если в качестве целевого языка указан Verilog.

symmetric_fir_tb_compile.vhd: Сценарий компиляции (команды vcom). Этот сценарий компилирует и загружает тестируемый объект (symmetric_fir.vhd) и код тестового стенда (symmetric_fir_tb.vhd)..

symmetric_fir_tb_sim.do: Mentor Graphics ModelSim скрипт для инициализации симулятора, настройки отображения сигнала волнового окна и запуска моделирования.

Для просмотра созданного кода тестового стенда в редакторе MATLAB дважды щелкните значок symmetric_fir_tb.vhd или symmetric_fir_tb.v в текущей папке.

Для проверки результатов моделирования можно использовать симулятор Mentor Graphics ModelSim. Убедитесь, что Mentor Graphics ModelSim уже установлен.

Для запуска симулятора используйте vsim (Проверка HDL). Эта команда показывает, как открыть симулятор, указав путь к исполняемому файлу:

vsim('vsimdir','C:\Program Files\ModelSim\questasim\10.6b\win64\vsim.exe')

Для компиляции и выполнения моделирования созданной модели и кода тестового стенда используются сценарии, создаваемые кодером HDL. Следующий пример иллюстрирует команды, которые компилируют и моделируют созданный тестовый стенд для sfir_fixed/symmetric_fir подсистема.

Откройте программное обеспечение Mentor Graphics ModelSim и перейдите в папку с ранее созданными файлами кода и сценариями.

QuestaSim>cd C:/work/sl_hdlcoder_work/hdlsrc

Созданный сценарий компиляции используется для компиляции и загрузки созданной модели и текстового кода стенда. Выполните эту команду для компиляции созданного кода.

QuestaSim>do symmetric_fir_tb_compile.do

Для выполнения моделирования используйте созданный сценарий моделирования. В следующем списке приведены команды и ответы. Любые предупреждающие сообщения можно игнорировать. Сообщение о завершении тестового стенда указывает на то, что моделирование завершено без ошибок сравнения. Эта команда используется для моделирования созданного кода.

QuestaSim>do symmetric_fir_tb_sim.do

Симулятор оптимизирует конструкцию и отображает результаты моделирования конструкции ЛПВП в волновом окне. если результаты моделирования не отображаются, откройте окно волны. Сценарий моделирования отображает входы и выходы в модели, включая сигналы синхронизации, сброса и включения синхронизации в окне волны.

Теперь можно просмотреть сигналы и убедиться, что результаты моделирования соответствуют функциям исходной конструкции. После проверки закройте симулятор Mentor Graphics ModelSim, а затем закройте файлы, открытые в редакторе MATLAB.