HDL Coder™ может сгенерировать код VHDL и Verilog из кода MATLAB®, моделей Simulink® и графиков Stateflow®. Можно затем проверить, что сгенерированный код совпадает исходным алгоритмом, и разверните его на целевом компьютере.

Этот пример иллюстрирует, как можно создать модель Simulink для генерации HDL-кода. Модель является простым алгоритмом суммирующего счетчика, который переносится назад, чтобы обнулить после того, как она достигает верхнего предела, который вы задаете.

StartMatlab. От панели инструментов MATLAB нажмите кнопку Simulink![]() . Затем в разделе HDL Coder выберите шаблон Blank DUT.

. Затем в разделе HDL Coder выберите шаблон Blank DUT.

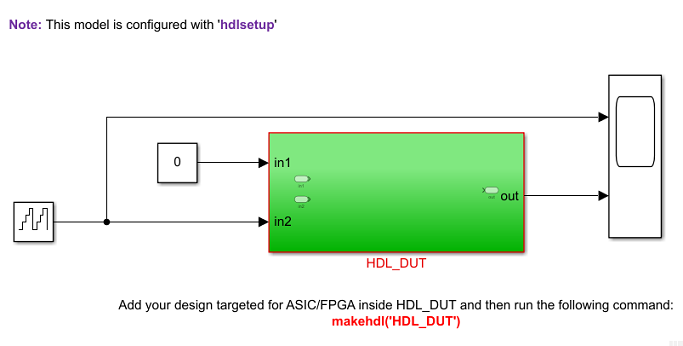

Выбор этого шаблона открывает модель Simulink, которая предварительно сконфигурирована для генерации HDL-кода. Сохраните модель с именем файла, таким как hdlcoder_simple_up_counter.slx в рабочей папке, которая перезаписываема.

Когда вы создаете модель для генерации HDL-кода, вы делите модель в Проект под тестом (DUT) и испытательный стенд. DUT является Подсистема, которая является в основном в верхнем уровне вашей модели и содержит алгоритм, для которого вы генерируете HDL-код. Блоки вне этой Подсистемы формируют испытательный стенд, и содержит входные параметры к Подсистеме и выходным значениям, которые регистрируются. Испытательный стенд гарантирует, что функциональность DUT как ожидалось.

Для испытательного стенда можно использовать блоки, которые не поддержаны для генерации HDL-кода. В шаблоне Blank DUT модель имеет Подсистему HDL_DUT, которая соответствует DUT. Блоки вне Подсистемы HDL_DUT формируют испытательный стенд. См. также Использование Шаблоны Simulink для генерации HDL-кода.

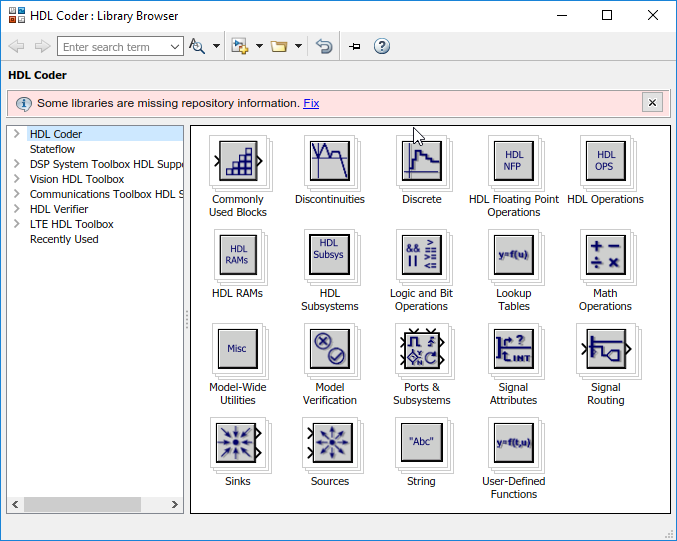

Откройте Библиотеку блоков HDL Coder для разработки вашего встречного алгоритма. Чтобы отфильтровать Браузер Библиотеки Simulink, чтобы показать библиотеки блоков что генерация HDL-кода поддержки, используйте функцию hdllib. В командной строке MATLAB, введите:

hdllib

В библиотеке HDL Coder вы видите несколько блоков, которые предварительно сконфигурированы для генерации HDL-кода. Блоки в этой библиотеке доступны с Simulink. Если у вас нет HDL Coder, вы можете моделировать блоки в своей модели, но не можете сгенерировать HDL-код.

Можно найти дополнительные поддержанные HDL блоки в этих библиотеках блоков:

Поддержка HDL DSP System Toolbox

Поддержка HDL Communications Toolbox

Vision HDL Toolbox

LTE HDL Toolbox

Восстановить Браузер Библиотеки к представлению по умолчанию, введите:

hdllib('off')Набор поддерживаемых блоков имеет тенденцию изменять каждый релиз. Восстановите свою поддерживаемую библиотеку блоков каждый раз, когда вы устанавливаете новую версию этого продукта.

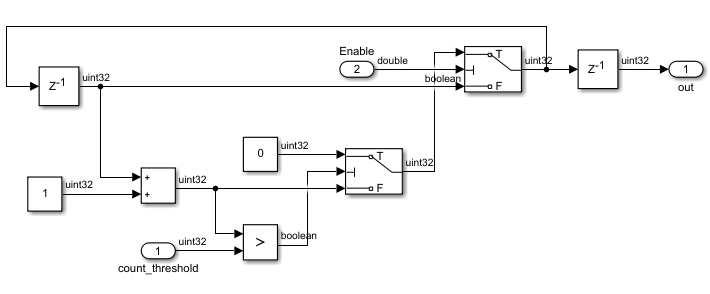

Дважды кликните Подсистему HDL_DUT. Перетащите блоки от библиотеки HDL Coder и добавьте их в свою модель. Эта таблица иллюстрирует блоки, чтобы добавить к вашей модели для разработки суммирующего счетчика. Узнать о том, что блок, и задавать параметры блоков для того блока, действительно дважды кликает блок.

| Блок | Библиотека | Количество блоков | Параметры блоков |

|---|---|---|---|

| Постоянный | Источники | 2 |

|

| Переключатель | Маршрутизация сигнала | 2 | Критерии передачи первого входа: u2> Порог |

| Задержка | Дискретный | 2 | Длина задержки: 1 |

| Добавление | Математические операции | 1 | Тип данных аккумулятора: Наследуйтесь: То же самое, как сначала введено |

| Оператор отношения | Логика и битовые операции | 1 | Оператор отношения:> |

Переименуйте входные порты In1 и In2 к count_threshold и Enable соответственно. Поместите блоки в свою модель и соедините их как показано в фигуре.

Сигнал Enable задает, должен ли счетчик рассчитать вверх от предыдущего значения. Когда сигнал Enable является логикой высоко, счетчик подсчитывает от нуля до значения count_threshold. Когда значение out становится равным значению count_threshold, счетчик переносится назад, чтобы обнулить и начинает рассчитывать снова. Когда сигнал Enable становится логикой низко, счетчик содержит предыдущее значение.

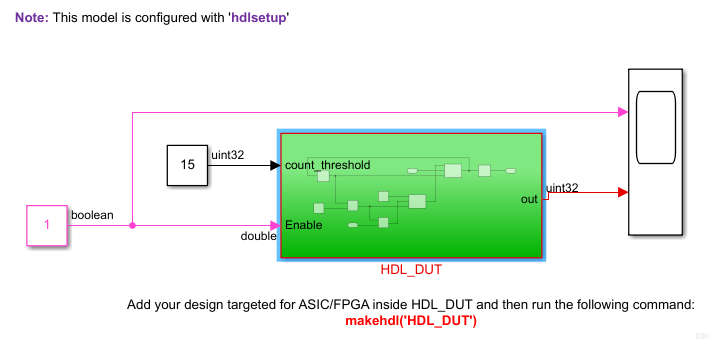

Перейдите к верхнему уровню модели и измените входные настройки.

Постоянный вход блока к count_threshold: Этот вход решает максимальное значение, до которого должен рассчитать счетчик. Этот пример иллюстрирует, как разработать 4-битный суммирующий счетчик. Поэтому установите Constant value на 15 (2^4 - 1) и установите Output data type на uint32.

Убедитесь, что тип выходных данных этого блока Константа совпадает с типом выходных данных блоков Константа в Подсистеме HDL_DUT.

Встречный вход блока Free-Running к Enable: В данном примере удалите блок Counter Free-Running. Замените этот блок на блок Constant, который имеет значение 1 и набора Output data type к boolean.

Эти данные показывают верхний уровень вашей модели после того, как вы применили эти настройки.

Чтобы узнать больше, как создать модель, смотрите, Создают Простую Модель (Simulink).

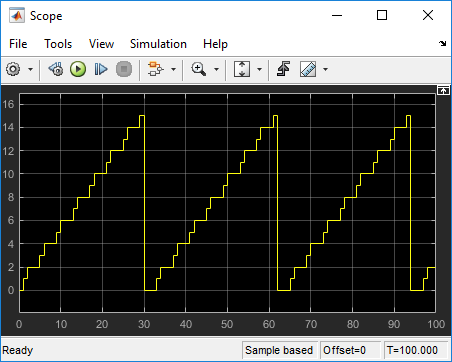

Моделируйте свою модель путем нажатия![]() кнопки. Чтобы видеть результаты симуляции, откройте блок Scope в верхнем уровне вашей модели. Результаты симуляции отображают сигнал

кнопки. Чтобы видеть результаты симуляции, откройте блок Scope в верхнем уровне вашей модели. Результаты симуляции отображают сигнал Enable в верхней части, генерирующей постоянное значение 1 и сигнала out, рассчитывающего от 0 до 15, затем переносясь назад, чтобы обнулить, и затем подсчитывая снова. Эта фигура отображает форму волны выходного сигнала out.

Вы теперь моделировали модель и проверили функциональность вашего проекта. Прежде чем вы сгенерируете HDL-код, необходимо проверить, что образцовые настройки совместимы для генерации HDL-кода. Чтобы сделать ваш проект совместимым для генерации HDL-кода, вы используете Средство проверки Модели HDL. Чтобы изучить, как использовать Средство проверки Модели HDL, смотрите Совместимость HDL Проверки Модели Используя Средство проверки Модели HDL.

checkhdl | hdllib | hdlmodelchecker | hdlsetup