Этот пример показывает, как можно использовать HDL Workflow Advisor, чтобы сгенерировать HDL-код и синтезировать проект на целевом Xilinx® FPGA.

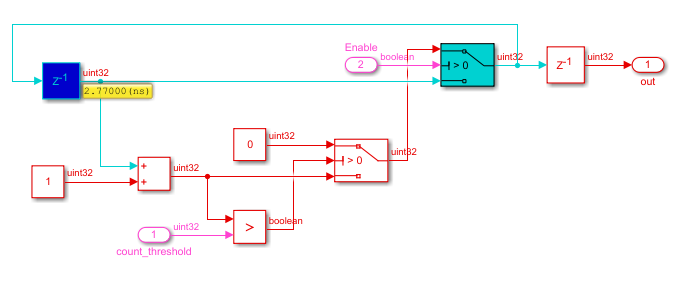

Для этого примера можно использовать простую модель суммирующего счетчика, которую вы создали как источник для генерации HDL-кода. Модель моделирует суммирующий счетчик, который рассчитывает от нуля до порогового значения и затем переносится назад, чтобы обнулить. Чтобы изучить, как создать эту модель, смотрите, Создают Модель Simulink для генерации HDL-кода.

Откройте эту модель, чтобы видеть простой суммирующий счетчик. Модель подсчитывает от нуля до порогового значения и затем переносится назад, чтобы обнулить. В этой модели пороговое значение установлено в 15. Можно изменить пороговое значение путем изменения значения блока Constant, который вводится к порту count_threshold. Разрешать сигнал задает, должен ли счетчик подсчитать или содержать предыдущее значение. Разрешать сигнал установлен в 1, что означает, что счетчик рассчитывает вверх постоянно.

open_system('hdlcoder_simple_up_counter.slx') set_param('hdlcoder_simple_up_counter', 'SimulationCommand', 'Update')

HDL Workflow Advisor проводит вас по этапам генерации HDL-кода для подсистемы Simulink® и процесса проектирования FPGA, таким как:

Проверка модели для совместимости генерации HDL-кода и автоматически фиксация несовместимых настроек.

Генерация HDL-кода, испытательного стенда и скриптов, чтобы создать и запустить код и испытательный стенд.

Генерация cosimulation или испытательных стендов SystemVerilog DPI и покрытия кода (требует HDL Verifier™).

Синтез и анализ синхронизации посредством интеграции со сторонними инструментами синтеза.

Обратная корректировка проекта модели с информацией о критическом пути и другой информацией получена во время синтеза.

Полные автоматизированные рабочие процессы для выбранных целевых устройств разработки FPGA и рабочий процесс ввода-вывода FPGA Simulink Real-Time™, включая FPGA в симуляции цикла.

Если вы не хотите синтезировать свой проект, но хотеть сгенерировать HDL-код, вы не должны устанавливать инструмент path. В HDL Workflow Advisor, на Set Target> шаг Set Target Device and Synthesis Tool, оставляют установку Synthesis tool No Synthesis Tool Specified по умолчанию, и затем запускают рабочий процесс.

Если вы хотите синтезировать свой проект на целевой платформе, прежде чем вы откроете HDL Workflow Advisor и запустите рабочий процесс, создадите путь к вашему инструменту Synthesis. Этот пример использует Xilinx Vivado, таким образом, вы, должно быть, уже установили Xilinx Vivado. Чтобы установить инструмент path, используйте функцию hdlsetuptoolpath, чтобы указать на установленный исполняемый файл Xilinx Vivado 2018.2. Чтобы узнать о последних поддерживаемых инструментах, смотрите Поддерживаемые Сторонние программы и Оборудование.

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath',... 'C:\Xilinx\Vivado\2018.2\bin\vivado.bat');

Опционально, можно использовать различный инструмент синтеза по вашему выбору и последовать этому примеру. Чтобы установить путь к тому инструменту синтеза, используйте hdlsetuptoolpath.

Запустить HDL Workflow Advisor с модели Simulink:

Из Редактора Simulink щелкните правой кнопкой по подсистеме DUT и выберите HDL Code> HDL Workflow Advisor.

Из командной строки выберите подсистему DUT и используйте функцию hdladvisor:

hdladvisor(gcb)

Когда вы открываете HDL Workflow Advisor, генератор кода может предупредить, что папка проекта несовместима. Чтобы открыть Советника, выберите Remove slprj and continue.

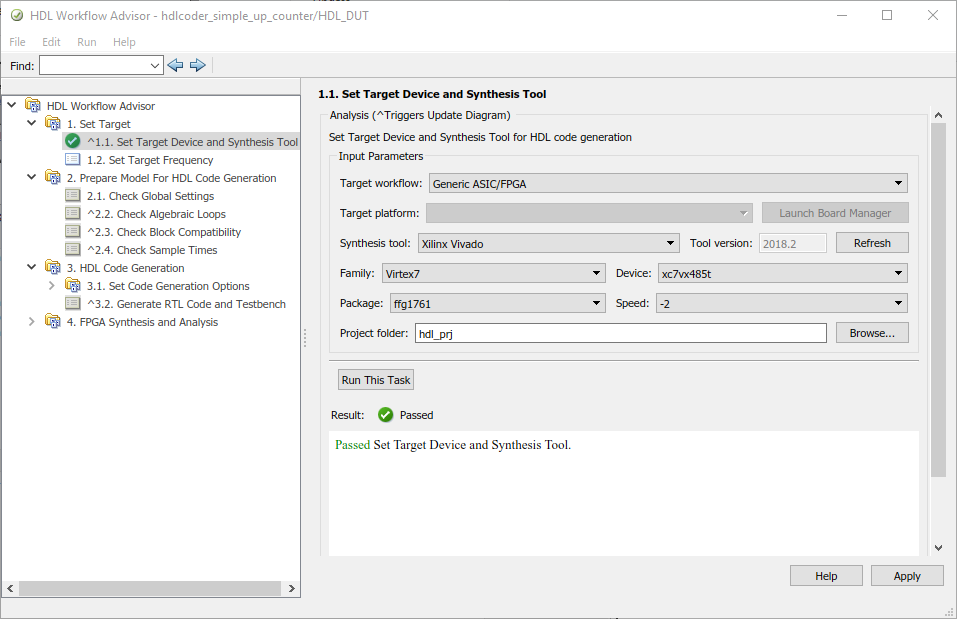

В HDL Workflow Advisor левая панель перечисляет папки в иерархии. Каждая папка представляет группу или категорию связанных задач. Расширение папок показывает доступные задачи в каждой папке. От левой панели можно выбрать папку или отдельную задачу. HDL Workflow Advisor отображает информацию о выбранной папке или задаче на правой панели. Содержимое правой панели зависит от выбранной папки или задачи. Для некоторых задач правая панель содержит простые средства управления для выполнения задачи и области отображения для сообщений о состоянии и других результатов задачи. Для других задач, которые включают код установки или параметры генерации испытательного стенда, правая панель отображает несколько параметров и настроек опции.

Чтобы узнать больше о каждой отдельной задаче, щелкните правой кнопкой по той задаче и выберите What's This?.

![]()

Чтобы узнать больше об окне HDL Workflow Advisor, смотрите Начало работы с HDL Workflow Advisor.

В Set Target> шаг Set Target Device and Synthesis Tool, для Synthesis tool, выбирает Xilinx Vivado и выбирает Run This Task.

В задаче Set Target Frequency задайте Целевую Частоту, которой вы хотите, чтобы проект достиг. В данном примере можно установить Target Frequency (MHz) на 200.

Оставьте все настройки, чтобы принять значение по умолчанию и щелкнуть правой кнопкой по задаче Check Sample Times и выбрать Run to Selected Task.

Путем выполнения задач в папке Prepare Model For HDL Code Generation HDL Workflow Advisor проверяет модель на совместимость генерации кода.

Если выполнение задачи генерирует предупреждение, выберите Modify All и повторно выполните задачу.

Чтобы изменить опции генерации кода, используйте задачи в Set Code Generation Options. Например, чтобы настроить целевой язык HDL и целевую папку генерации кода, используйте задачу Set Basic Options. После того, как вы внесете изменения, нажмите Apply.

Чтобы сгенерировать код, щелкните правой кнопкой по задаче Generate RTL Code and Testbench и выберите Run to Selected Task.

Если вы хотите сгенерировать испытательный стенд HDL или модель валидации, можно задать соответствующие настройки в задаче Generate RTL Code and Testbench. Чтобы задать дополнительные опции испытательного стенда, используйте задачу Set Testbench Options.

В FPGA Synthesis and Analysis> Perform Synthesis and P/R> задача Perform Place and Route, отменяйте Skip this task и нажмите Apply.

Щелкните правой кнопкой по Annotate Model with Synthesis Result и выберите Run to Selected Task.

Просмотрите аннотируемый критический путь в модели.

Чтобы запустить рабочий процесс HDL в командной строке, можно экспортировать настройки Workflow Advisor в скрипт. Чтобы экспортировать в скрипт, в окне HDL Workflow Advisor, выбирают File> Export to Script. В диалоговом окне Export Workflow Configuration введите имя файла и сохраните скрипт.

Скрипт является файлом MATLAB®, который можно запустить из командной строки. Можно изменить скрипт непосредственно или, импортировать скрипт в HDL Workflow Advisor, изменить задачи и экспортировать обновленный скрипт. Чтобы узнать больше, смотрите Рабочий процесс HDL Выполнения со Скриптом.

hdladvisor | hdlsetuptoolpath | makehdl