В этом примере показано, как сгенерировать испытательный стенд HDL и проверить сгенерированный код для вашего проекта. Пример принимает, что у вас уже есть сгенерированный HDL-код для вашей модели. Если у вас уже нет сгенерированного HDL-кода, можно все еще открыть эту модель и сгенерировать испытательный стенд HDL. Прежде, чем сгенерировать испытательный стенд, HDL Coder™ запускает генерацию кода, чтобы убедиться, что существует по крайней мере одна успешная генерация кода, запущенная прежде, чем сгенерировать испытательный стенд.

Этот пример иллюстрирует, как проверить сгенерированный код для КИХ-модели фильтра. Чтобы изучить, как сгенерировать HDL-код, смотрите, Генерируют HDL-код из Модели Simulink из Командной строки.

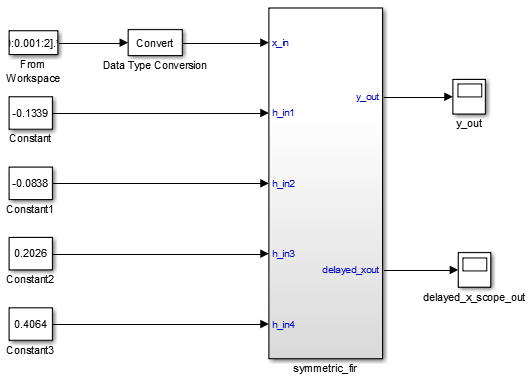

Этот пример использует Симметричную КИХ-модель фильтра, которая совместима для генерации HDL-кода. Открыть эту модель в командной строке, введите:

sfir_fixed

Модель использует разделение труда, которое подходит для проекта HDL.

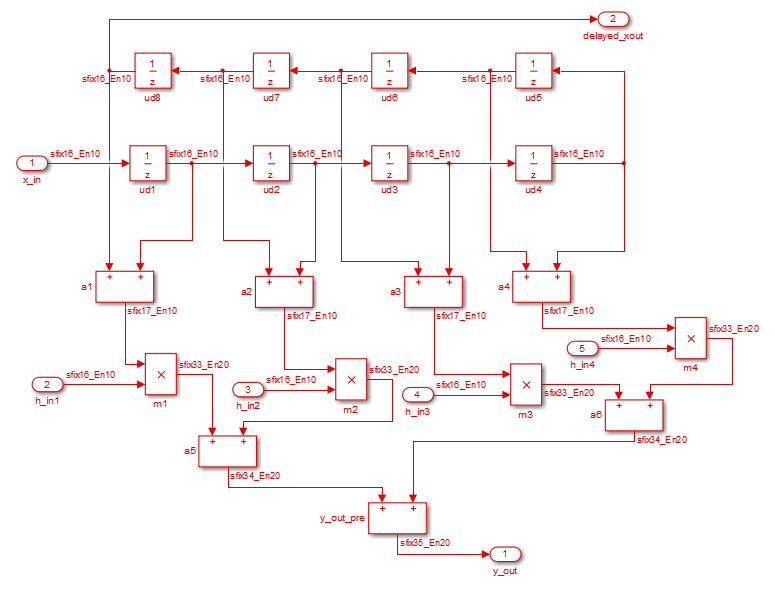

symmetric_fir подсистема, которая реализует алгоритм фильтра, является устройством под тестом (DUT). Сущность HDL сгенерирована от этой подсистемы.

Компоненты модели верхнего уровня, которые управляют подсистемой, работают испытательным стендом.

Модель верхнего уровня генерирует 16-битные входные сигналы фиксированной точки для symmetric_fir подсистема. Блок Signal From Workspace генерирует тестовое воздействие (стимул) сигнал для фильтра. Четыре блока Constant обеспечивают коэффициенты фильтра. Блоки Scope используются для симуляции и не используются для генерации HDL-кода.

Перейти к symmetric_fir подсистема, введите:

open_system('sfir_fixed/symmetric_fir')

В MATLAB®:

Создайте папку под названием sl_hdlcoder_work, например:

mkdir C:\work\sl_hdlcoder_work

sl_hdlcoder_work хранит локальную копию модели в качестве примера и папок и сгенерированного HDL-кода. Используйте местоположение папки, которое не является в дереве папки MATLAB.

Сделайте sl_hdlcoder_work папка ваша рабочая папка, например:

cd C:\work\sl_hdlcoder_workСохраните локальную копию sfir_fixed модель к вашей текущей рабочей папке. Оставьте модель открытой.

Чтобы проверить функциональность HDL-кода, который вы сгенерировали для DUT, сгенерируйте испытательный стенд HDL. Испытательный стенд включает:

Данные о стимуле, сгенерированные источниками сигнала, соединенными с сущностью под тестом.

Выходные данные сгенерированы сущностью под тестом. Во время запущенного испытательного стенда эти данные сравниваются с выходными параметрами кода VHDL® в целях верификации.

Синхронизируйте, сбросьте, и часы позволяют входным параметрам управлять сущностью под тестом.

Инстанцирование компонента сущности под тестом.

Код, чтобы управлять сущностью под тестом и сравнить его выходные параметры с ожидаемыми данными.

Можно симулировать сгенерированный испытательный стенд и файлы скрипта со средством моделирования Mentor Graphics® ModelSim®.

Этот пример иллюстрирует, как сгенерировать испытательный стенд HDL, чтобы симулировать и проверить сгенерированный HDL-код для вашего проекта. Можно также проверить сгенерированный HDL-код из модели с помощью этих методов:

| Метод верификации | Для получения дополнительной информации |

|---|---|

| Модель валидации | Сгенерированная модель модели и валидации |

| Cosimulation HDL (требует HDL Verifier™), | Cosimulation |

| Испытательный стенд SystemVerilog DPI (требует HDL Verifier), | Испытательный стенд SystemVerilog DPI |

| FPGA в цикле (требует HDL Verifier), | FPGA в цикле |

В зависимости от того, сгенерировали ли вы код VHDL или Verilog, сгенерируйте код испытательного стенда VHDL или Verilog. Код испытательного стенда управляет HDL-кодом, который вы сгенерировали для DUT. По умолчанию HDL-код и код испытательного стенда записаны в ту же целевую папку hdlsrc относительно текущей папки.

Чтобы сгенерировать код испытательного стенда и скрипты для компиляции и симуляции, используйте makehdltb функция. В командной строке, введите:

makehdltb('sfir_fixed/symmetric_fir')

Чтобы задать индивидуальные настройки, прежде чем вы сгенерируете код испытательного стенда, используйте hdlset_param функция. Можно также задать различные аргументы пары "имя-значение" с makehdltb функция, чтобы настроить опции генерации HDL-кода при генерации HDL-кода. Например, чтобы сгенерировать код испытательного стенда Verilog, используйте TargetLanguage свойство.

makehdltb('sfir_fixed/symmetric_fir', 'TargetLanguage', 'Verilog')

hdlset_param, установите этот параметр на модели и затем запуститесь makehdltb функция.hdlset_param('sfir_fixed', 'TargetLanguage', 'Verilog') makehdltb('sfir_fixed/symmetric_fir')

Если у вас уже нет сгенерированного кода для вашей модели, HDL Coder компилирует модель и генерирует HDL-код прежде, чем сгенерировать испытательный стенд. В зависимости от параметров отображения модели, таких как типы данных порта, модель может изменение внешности после генерации кода.

В то время как генерация испытательного стенда продолжает, HDL Coder отображает сообщения о ходе выполнения. Процесс должен вместе с сообщением

### HDL TestBench Generation Complete.

После генерации испытательного стенда вы видите сгенерированные файлы в hdlsrc папка.

symmetric_fir_tb.vhd: Код испытательного стенда VHDL, со сгенерированными тестовыми и выходными данными. Если вы сгенерировали код испытательного стенда Verilog, сгенерированным файлом является symmetric_fir_tb.v.

symmetric_fir_tb_pkg.vhd: Файл пакета для кода испытательного стенда VHDL. Этот файл не сгенерирован, если вы задали Verilog как выходной язык.

symmetric_fir_tb_compile.vhd: Скрипт компиляции (vcom команды). Этот скрипт компилирует и загружает сущность, которая будет протестирована (symmetric_fir.vhd) и код испытательного стенда (symmetric_fir_tb.vhd)..

symmetric_fir_tb_sim.do: Скрипт Mentor Graphics ModelSim, чтобы инициализировать средство моделирования, настройте отображения сигнала окна волны и запустите симуляцию.

Чтобы просмотреть сгенерированный код испытательного стенда в редакторе MATLAB, дважды кликните symmetric_fir_tb.vhd или symmetric_fir_tb.v файл в текущей папке.

Чтобы проверить результаты симуляции, можно использовать средство моделирования Mentor Graphics ModelSim. Убедитесь, что вы уже установили Mentor Graphics ModelSim.

Чтобы запустить средство моделирования, используйте vsim (HDL Verifier) функция. Эта команда показывает, как открыть средство моделирования путем определения пути к исполняемому файлу:

vsim('vsimdir','C:\Program Files\ModelSim\questasim\10.6b\win64\vsim.exe')

Чтобы скомпилировать и запустить симуляцию сгенерированного кода и испытательного стенда модели, используйте скрипты, которые сгенерированы HDL Coder. Следование примеру иллюстрирует команды, которые компилируют и симулируют сгенерированный испытательный стенд для sfir_fixed/symmetric_fir подсистема.

Откройте программное обеспечение Mentor Graphics ModelSim и перейдите к папке, которая имеет ранее файлы сгенерированного кода и скрипты.

QuestaSim>cd C:/work/sl_hdlcoder_work/hdlsrc

Используйте сгенерированный скрипт компиляции, чтобы скомпилировать и загрузить сгенерированный код места размещения модели и текста. Запустите эту команду, чтобы скомпилировать сгенерированный код.

QuestaSim>do symmetric_fir_tb_compile.do

Используйте сгенерированный скрипт симуляции, чтобы выполнить симуляцию. Следующий листинг показывает команду и ответы. Можно проигнорировать любые предупреждающие сообщения. Сообщение завершения испытательного стенда указывает, что симуляция выполнение до завершения без ошибок сравнения. Запустите эту команду, чтобы симулировать сгенерированный код.

QuestaSim>do symmetric_fir_tb_sim.do

Средство моделирования оптимизирует ваш проект и отображает результаты симуляции вашего проекта HDL в окне wave. если вы не видите результаты симуляции, открываете окно wave. Скрипт симуляции отображает вводы и выводы в модели включая сигналы тактовой частоты, сбросы и сигналы разрешения действии по сигналу тактовой частоты в окне wave.

Можно теперь просмотреть сигналы и проверить, что результаты симуляции совпадают с функциональностью первоначального проекта. После проверки близко средство моделирования Mentor Graphics ModelSim, и затем закрывает файлы, которые вы открыли в редакторе MATLAB.