Быстрое создание прототипа IP-ядра HDL путем взаимодействия с целевой платой через Ethernet или JTAG. Используйте Ethernet-соединение для плат с процессором ARM. Используйте соединение JTAG для плат, не имеющих процессора ARM.

Целевая платформа, например, ZedBoard™, на которой развертывается модель интерфейса программного обеспечения

Последняя версия стороннего средства синтеза, например, Xilinx ® Vivado ®. См. раздел Языковая поддержка HDL и поддерживаемые сторонние инструменты и оборудование. В сессии MATLAB ® задайте путь к установленному инструменту синтеза с помощью hdlsetuptoolpath функция.

Чтобы использовать Ethernet-подключение к целевым аппаратным платам со встроенным процессором ARM, можно либо создать сценарий программного интерфейса, либо создать пользовательский сценарий программного обеспечения. Перед установкой интерфейса на основе Ethernet установите на карте SD платы образ микропрограммного обеспечения MathWorks ®. Для настройки образа микропрограммного обеспечения для целевой платы:

Для получения информации о системных платах Intel ® см. раздел Настройка управляемой SD-карты (пакет поддержки кодера HDL для устройств Intel SoC)

Для получения информации о платах, связанных с Xilinx, см. раздел Настройка управляемой SD-карты (пакет поддержки кодера HDL для платформы Xilinx Zynq).

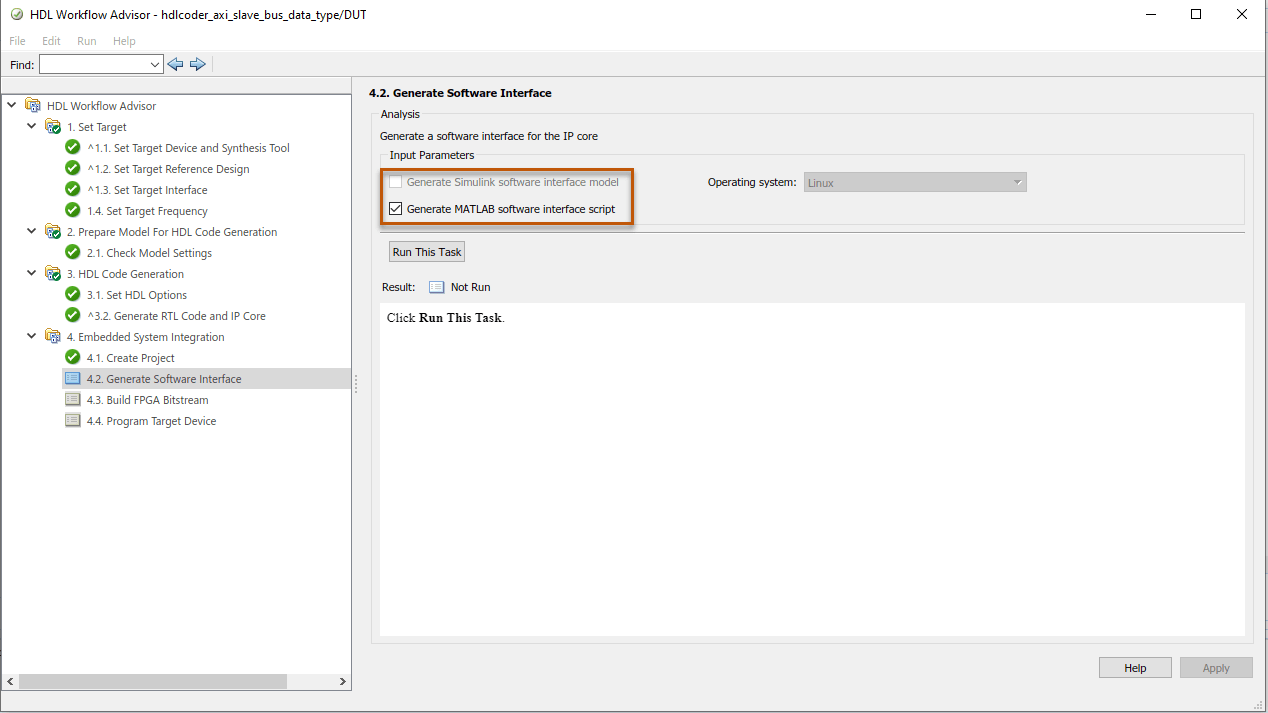

При выполнении задачи Генерировать программный интерфейс (Generate Software Interface) установите флажок Генерировать сценарий программного интерфейса MATLAB (Generate MATLAB software interface script).

Генерируемые файлы MATLAB:

gs_modelName_setup.m, который представляет собой сценарий установки, добавляющий AXI4 подчиненный и AXI4-Stream интерфейсы. Сценарий также содержит объекты порта DUT, которые имеют имя порта, направление, тип данных и информацию о сопоставлении интерфейса. Затем сценарий сопоставляет порты DUT с соответствующими интерфейсами.

gs_modelName_interface.m, который создает целевой объект, создает экземпляр сценария установки gs_modelName_setup.m, а затем подключается к целевому оборудованию. Затем сценарий посылает команды чтения и записи в сформированное ядро IP HDL.

См. раздел Создание сценария интерфейса программного обеспечения для проверки и быстрого создания прототипа IP-ядра HDL.

Для быстрого создания прототипов настройте сценарий интерфейса программного обеспечения или создайте собственный сценарий на основе изменения исходного проекта. Настройте сценарий, чтобы указать:

Целевой объект для другого поставщика FPGA.

Дополнительные интерфейсы или настройка существующих интерфейсов на основе изменений исходного проекта. HDL Coder™ использует эту информацию для создания драйверов IIO для доступа к ядру IP HDL.

Дополнительные объекты порта DUT или удаление существующих объектов в зависимости от способа изменения конструкции, а затем соответствующее изменение информации о сопоставлении.

Входные данные для записи в порты DUT и выходные данные для считывания из портов.

Можно настроить созданный сценарий программного обеспечения или создать собственный сценарий интерфейса программного обеспечения. Чтобы создать пользовательский сценарий программного обеспечения, выполните следующие действия.

Создание fpga объект для целевого устройства и сохранить в hFPGA.

hFPGA = fpga("Xilinx")

hFPGA =

fpga with properties:

Vendor: "Xilinx"

Interfaces: [0×0 fpgaio.interface.InterfaceBase]

Использование целевого объекта Intel:

hFPGA = fpga("Intel")

hFPGA =

fpga with properties:

Vendor: "Intel"

Interfaces: [0×0 fpgaio.interface.InterfaceBase]

Сконфигурируйте интерфейсы AXI для сопоставления портов DUT в сгенерированном ядре IP HDL. Можно добавить AXI4 подчиненные и AXI4-Stream интерфейсы. Для добавления AXI4 подчиненных интерфейсов используйте addAXI4SlaveInterface функция.

addAXI4SlaveInterface(hFPGA, ... ... % Interface properties "InterfaceID", "AXI4-Lite", ... "BaseAddress", 0xA0000000, ... "AddressRange", 0x10000, ... ... % Driver properties "WriteDeviceName", "mwipcore0:mmwr0", ... "ReadDeviceName", "mwipcore0:mmrd0");

Для добавления AXI4-Stream интерфейсов используйте addAXI4StreamInterface функция.

addAXI4StreamInterface(hFPGA, ... ... % Interface properties "InterfaceID", "AXI4-Stream", ... "WriteEnable", true, ... "ReadEnable", true, ... "WriteFrameLength", 1024, ... "ReadFrameLength", 1024, ... ... % Driver properties "WriteDeviceName", "mwipcore0:mm2s0", ... "ReadDeviceName", "mwipcore0:s2mm0");

Указанная информация о сопоставлении интерфейса сохраняется как свойство в fpga объект, hFPGA.

hFPGA

hFPGA =

fpga with properties:

Vendor: "Xilinx"

Interfaces: [1×2 fpgaio.interface.InterfaceBase]Для автономных плат FPGA, не имеющих встроенного процессора ARM, можно создать объект, а затем использовать aximaster объект. Затем используйте этот объект в качестве драйвера для addAXI4SlaveInterface функция. aximaster требуется пакет поддержки HDL Verifier™ для платы Intel или Xilinx FPGA.

% Create an "aximaster" object hAXIMDriver = aximaster("Xilinx"); % Pass it into the addInterface command addAXI4SlaveInterface(hFPGA, ... ... % Interface properties "InterfaceID", "AXI4-Lite", ... "BaseAddress", 0xB0000000, ... "AddressRange", 0x10000, ... ... % Driver properties "WriteDriver", hAXIMDriver, ... "ReadDriver", hAXIMDriver, ... "DriverAddressMode", "Full");

Укажите информацию о портах DUT в сгенерированном IP-ядре HDL в качестве массива объектов портов с помощью hdlcoder.DUTPort объект. Объект представляет порты DUT на целевом оборудовании.

hPort_h_in1 = hdlcoder.DUTPort("h_in1", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Lite", ... "IOInterfaceMapping", "0x100")

hPort_h_in1 =

DUTPort with properties:

Name: "h_in1"

Direction: IN

DataType: [1×1 embedded.numerictype]

Dimension: [1 1]

IOInterface: "AXI4-Lite"

IOInterfaceMapping: "0x100"Для записи или чтения из портов DUT в сгенерированном IP-ядре HDL сопоставьте порты интерфейсу AXI с помощью mapPort функция. После сопоставления портов с интерфейсами эта информация сохраняется на fpga объект в качестве Interfaces собственность.

mapPort(hFPGA, hPort_h_in1); hFPGA.Interfaces

ans =

AXI4Slave with properties:

InterfaceID: "AXI4-Lite"

BaseAddress: "0xA0000000"

AddressRange: "0x10000"

WriteDriver: [1×1 fpgaio.driver.AXIMemoryMappedIIOWrite]

ReadDriver: [1×1 fpgaio.driver.AXIMemoryMappedIIORead]

InputPorts: "h_in1"

OutputPorts: [0×0 string]

Можно также указать эту информацию для портов, сопоставленных с AXI4-Stream интерфейсами.

hPort_x_in_data = hdlcoder.DUTPort("x_in_data", ... "Direction", "IN", ... "DataType", numerictype(1,16,10), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Stream"); hPort_y_out_data = hdlcoder.DUTPort("y_out_data", ... "Direction", "OUT", ... "DataType", numerictype(1,32,20), ... "Dimension", [1 1], ... "IOInterface", "AXI4-Stream");

Для записи или чтения из портов DUT в сгенерированном IP-ядре HDL сопоставьте порты интерфейсу AXI с помощью mapPort функция.

mapPort(hFPGA, [hPort_x_in_data, hPort_y_out_data]);

fpga объект в качестве Interfaces собственность.hFPGA

hFPGA =

fpga with properties:

Vendor: "Xilinx"

Interfaces: [1×2 fpgaio.interface.InterfaceBase]hFPGA.Interfaces

ans =

AXI4Slave with properties:

InterfaceID: "AXI4-Lite"

BaseAddress: "0xA0000000"

AddressRange: "0x10000"

WriteDriver: [1×1 fpgaio.driver.AXIMemoryMappedIIOWrite]

ReadDriver: [1×1 fpgaio.driver.AXIMemoryMappedIIORead]

InputPorts: "h_in1"

OutputPorts: [0×0 string]

AXI4Stream with properties:

InterfaceID: "AXI4-Stream"

WriteEnable: 1

ReadEnable: 1

WriteFrameLength: 1024

ReadFrameLength: 1024

WriteDriver: [1×1 fpgaio.driver.AXIStreamIIOWrite]

ReadDriver: [1×1 fpgaio.driver.AXIStreamIIORead]

InputPorts: "x_in_data"

OutputPorts: "y_out_data"

Для тестирования основных функций HDL IP используйте readPort и writePort позволяет записывать данные на эти порты или считывать данные с этих портов.

writePort(hFPGA, "h_in1", 5); writePort(hFPGA, "x_in", sin(linspace(0, 2*pi, 1024))); data = readPort(hFPGA, "y_out");

После тестирования IP-ядра HDL можно освободить аппаратный ресурс, связанный с fpga с помощью release функция.

release(hFPGA)

Пример создания сценария пользовательского интерфейса и прототипирования проекта на целевой плате FPGA по Ethernet-соединению см. в разделе Прототип проектирования FPGA на оборудовании с использованием оперативных данных с помощью команд MATLAB.

Для автономных плат FPGA, не имеющих встроенного процессора ARM, в эталонную конструкцию можно вставить JTAG MATLAB в качестве AXI Master IP. Создание сценария, использующего aximaster объект, который подключается к IP по физическому кабелю JTAG. Этот сценарий позволяет выполнять команды чтения и записи в области памяти подчиненных устройств из командной строки MATLAB.

Для использования MATLAB в качестве хозяина AXI:

Установите пакеты поддержки оборудования HDL Verifier.

Не ставьте перед собой автономные платы, не имеющие hRD.AXI4SlaveInterface функциональные возможности или платы, основанные на Xilinx ISE.

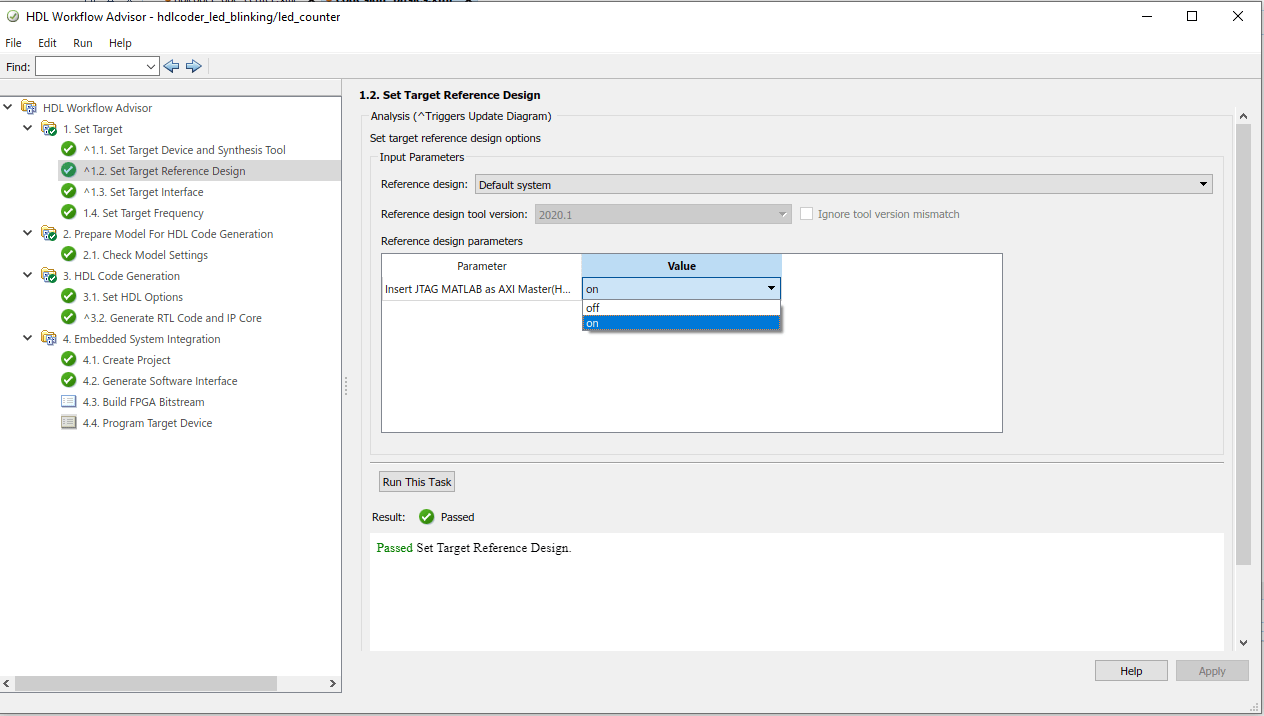

При запуске рабочего процесса создания IP-ядра в задании «Задать цель > Задать целевое ссылочное проектирование» выберите «Система по умолчанию» для параметра «Ссылочное проектирование» и установите для параметра «Вставить JTAG MATLAB как AXI Master» значение «вкл».

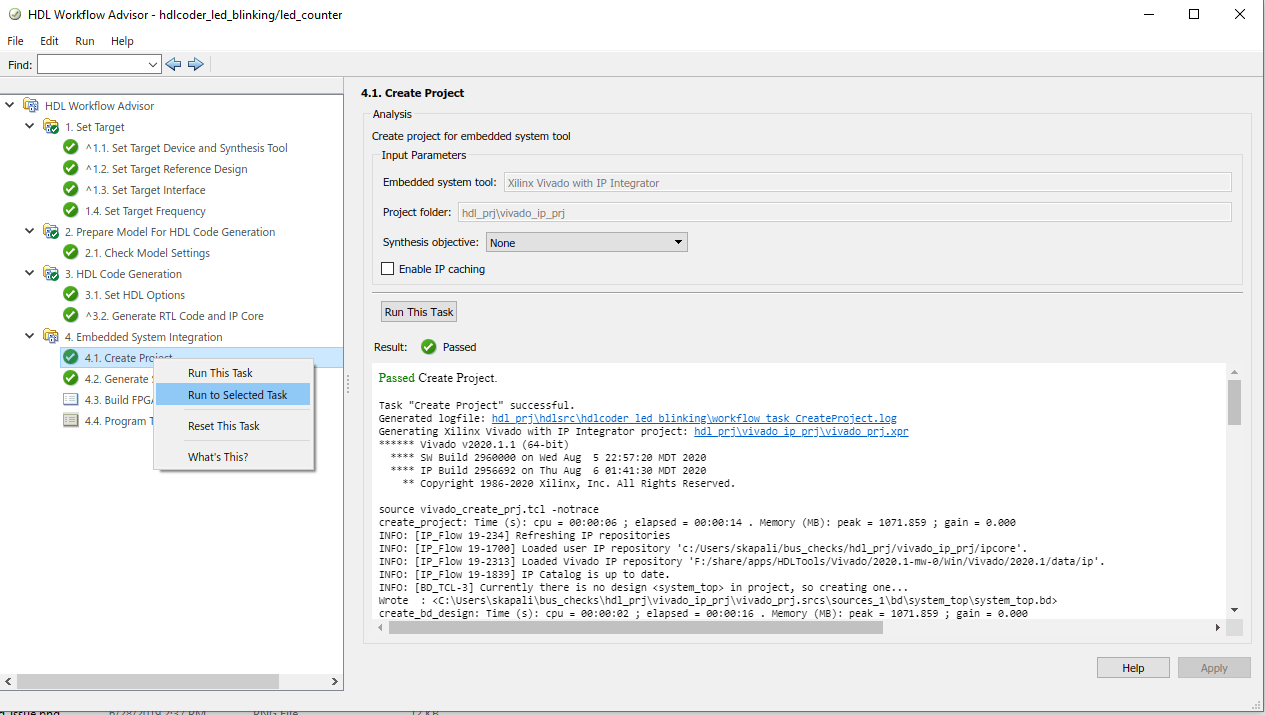

Чтобы создать ядро IP и создать проект с помощью AXI Master IP, щелкните правой кнопкой мыши задачу Создать проект (Create Project) и выберите Выполнить до выбранной задачи (Run to Selected Task).

Теперь можно взаимодействовать с целевой платой FPGA с помощью функции JTAG MATLAB в качестве AXI Master. Создание объекта с помощью aximaster объект. Использовать созданный объект в качестве драйвера для addAXI4SlaveInterface функция.

% Create an "aximaster" object hAXIMDriver = aximaster("Xilinx"); % Pass it into the addInterface command addAXI4SlaveInterface(hFPGA, ... ... % Interface properties "InterfaceID", "AXI4-Lite", ... "BaseAddress", 0xB0000000, ... "AddressRange", 0x10000, ... ... % Driver properties "WriteDriver", hAXIMDriver, ... "ReadDriver", hAXIMDriver, ... "DriverAddressMode", "Full");

Пример взаимодействия с целевой платой через JTAG см. в разделе Использование JTAG MATLAB в качестве AXI Master для управления генерируемым ядром IP кодера HDL.