При запуске рабочего процесса совместного проектирования аппаратного и программного обеспечения для платформ SoC создается IP-ядро HDL для алгоритма DUT, а затем выполняется интеграция IP-ядра в эталонный проект. См. раздел Рабочий процесс совместного проектирования аппаратного и программного обеспечения для платформ SoC.

Для тестирования IP-ядра HDL на целевом оборудовании создайте модель программного интерфейса. Модель программного интерфейса использует блоки драйверов AXI для тестирования основных функций HDL IP при моделировании внешнего режима.

Целевая платформа, например, ZedBoard, на которой требуется развернуть модель интерфейса программного обеспечения.

Последняя версия стороннего средства синтеза, например, Xilinx ® Vivado ®. См. раздел Языковая поддержка HDL и поддерживаемые сторонние инструменты и оборудование. В сессии MATLAB ® задайте путь к установленному инструменту синтеза с помощью hdlsetuptoolpath функция.

При создании модели программного интерфейса установите Embedded Coder ® и Simulink ® Coder™.

Установите пакеты поддержки HDL Coder™ и Embedded Coder для целевой платформы. На панели инструментов MATLAB нажмите кнопку Главная > Надстройки > Получить надстройки. См. раздел Получение надстроек и управление ими.

При выполнении рабочего процесса генерации IP-ядра можно создать сценарий и модель интерфейса программного обеспечения из пользовательского интерфейса помощника по рабочим процессам HDL или в командной строке.

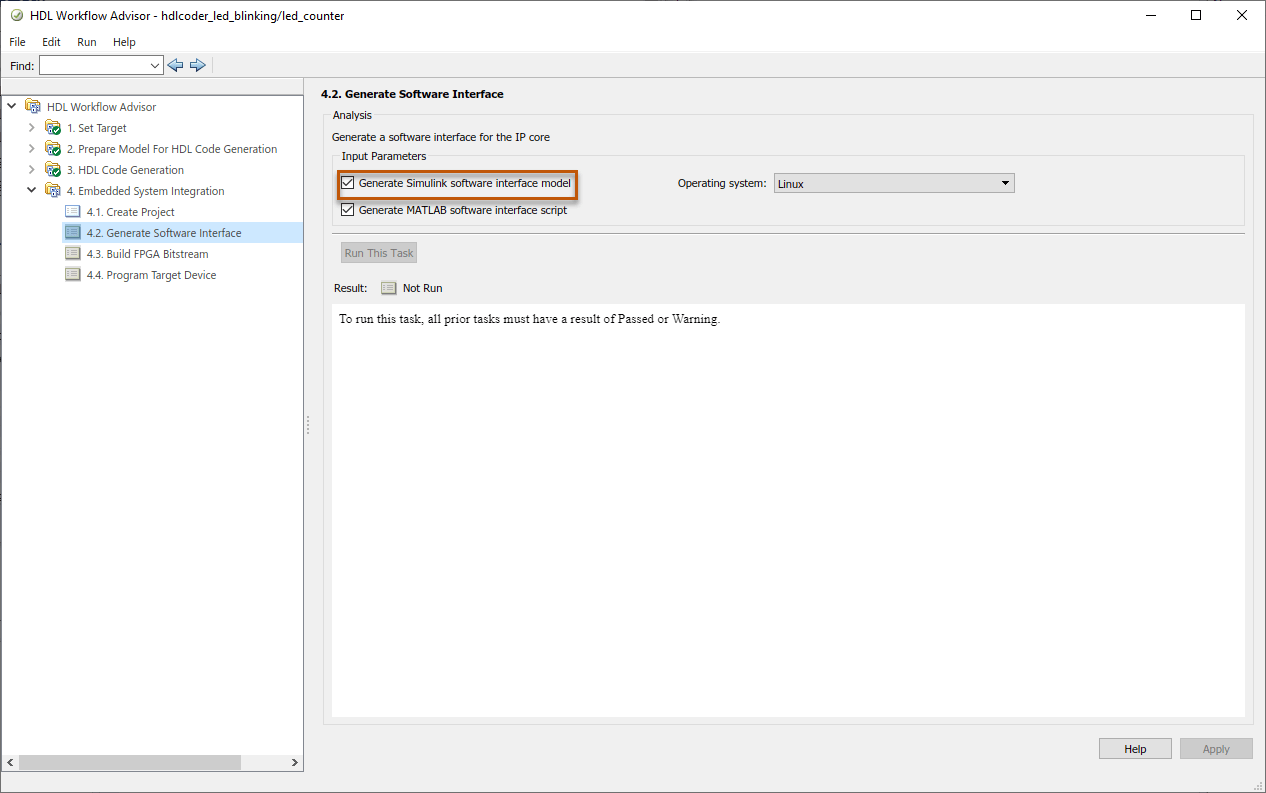

В пользовательском интерфейсе в задаче Интеграция встроенных систем > Создание интерфейса программного обеспечения установите флажок Генерировать модель интерфейса программного обеспечения.

При использовании автономных плат FPGA невозможно создать модель интерфейса программного обеспечения. Вместо этого можно создать сценарий программного интерфейса и протестировать ядро IP с помощью драйвера MATLAB AXI Master.

В задаче Задать целевое ссылочное проектирование (Set Target Reference Design) установите для команды Вставить JTAG MATLAB (Insert JTAG MATLAB) значение Мастер AXI (AXI Master) значение on Запустите рабочий процесс для задачи «Создать программный интерфейс».

В задаче «Создать программный интерфейс» установите флажок «Создать сценарий программного интерфейса» и запустите эту задачу.

В командной строке экспортируйте параметры помощника по рабочим процессам HDL в сценарий, а затем используйте эти свойства с объектом «Конфигурация рабочего процесса». Этот сценарий определяет выполнение задачи программного интерфейса путем создания модели и сценария. Если пропустить задачу, установив для параметра RunTaskGenerateGroupInterface значение false, модель и сценарий не будут созданы. См. раздел Настройка и запуск рабочего процесса создания ядра IP со сценарием.

% Export Workflow Configuration Script % ... %% Load the Model load_system('hdlcoder_led_blinking'); %% Model HDL Parameters % Set Model HDL parameters % ... hdlset_param('hdlcoder_led_blinking', 'SynthesisTool', 'Xilinx Vivado'); hdlset_param('hdlcoder_led_blinking', 'Workflow', 'IP Core Generation'); % ... % Set Workflow tasks to run hWC.RunTaskGenerateSoftwareInterface = true; hWC.GenerateSoftwareInterfaceModel = true; hWC.GenerateSoftwareInterfaceScript = true; % ... %% Run the workflow hdlcoder.runWorkflow('hdlcoder_led_blinking/led_counter', hWC);

При запуске рабочего процесса для платформ SoC создается модель программного интерфейса для тестирования основных функций HDL IP. Если установлены Embedded Coder и Simulink Coder, можно создать внедренный код из модели, построить и запустить исполняемый файл на ARM-процессоре. При назначении автономных плат FPGA невозможно создать модель интерфейса программного обеспечения, поскольку платы не имеют встроенного процессора ARM. Вместо этого создайте сценарий программного интерфейса для тестирования ядра IP с помощью MATLAB AXI Master.

Созданная модель интерфейса программного обеспечения заменяет алгоритм DUT в исходной модели блоками драйверов AXI, основанными на таблице интерфейса целевой платформы и настройках эталонного дизайна. Для тестирования основных функций HDL IP смоделировать модель во внешнем режиме для запуска на целевом оборудовании. По умолчанию в модели включено параллельное выполнение, что означает, что несколько задач выполняются одновременно процессором на платформе SoC.

Модель интерфейса программного обеспечения имеет то же имя, что и исходная модель с префиксом gm_ и постфикс _interface. Сгенерированная модель из генерации кода HDL имеет префикс gm_. Чтобы указать, что эта модель используется в качестве модели интерфейса программного обеспечения, измените префикс на sm_.

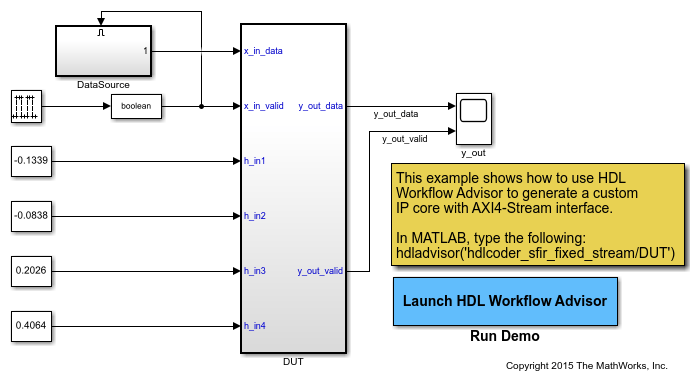

Открытие модели hdlcoder_sfir_fixed_stream. Эта модель отображает sfir_fixed в упрощенный протокол AXI4-Stream путем вставки Valid сигнал в качестве входного управляющего порта.

open_system('hdlcoder_sfir_fixed_stream')

Откройте помощник по рабочим процессам HDL для подсистемы DUT. В задании Set Target Device and Synthesis Tool укажите IP Core Generation как целевой рабочий процесс и ZedBoard как целевая платформа. Щелкните Запустить эту задачу.

В задаче «Задать целевую ссылочную конструкцию» укажите систему по умолчанию с AXI4-Stream интерфейсом в качестве целевой ссылочной конструкции. Щелкните Запустить эту задачу.

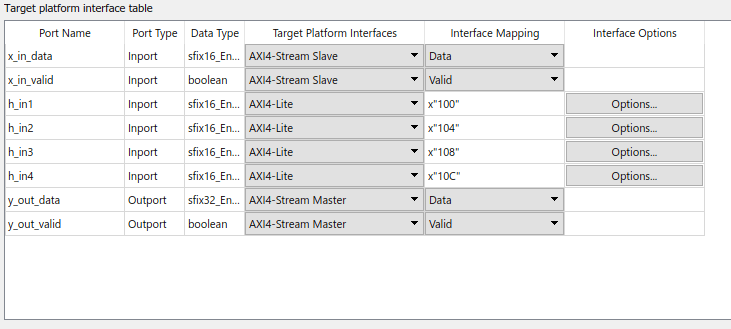

В задаче Set Target Interface сопоставьте порты DUT с целевыми интерфейсами в таблице Target platform interface. Щелкните Запустить эту задачу.

Щелкните правой кнопкой мыши задачу Создать программный интерфейс (Generate Software Interface) и выберите Выполнить с выбранной задачей (Run to selected task). Запустите рабочий процесс для создания модели интерфейса программного обеспечения.

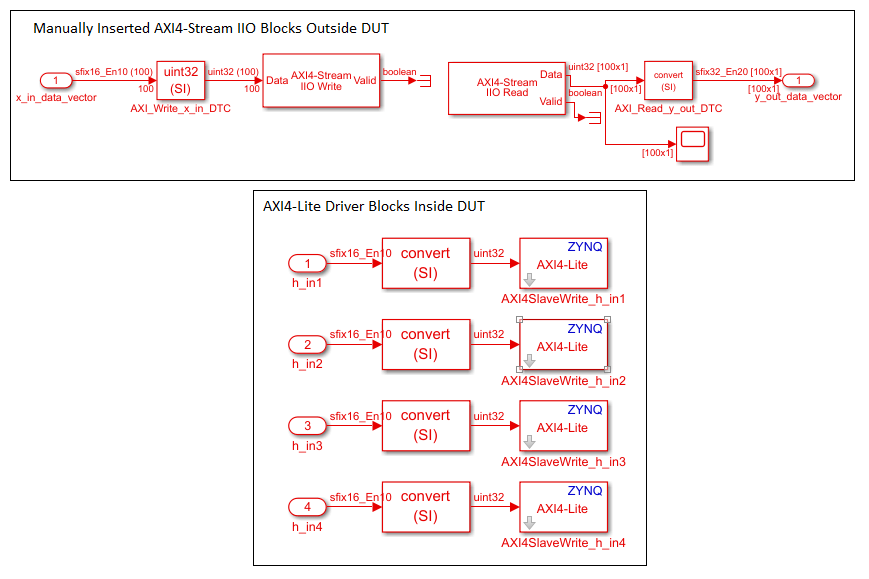

Созданная модель интерфейса программного обеспечения имеет имя gm_hdlcoder_sfir_fixed_stream_interface.slx. Поскольку исходная модель использует скалярные порты для портов данных x_in_data и y_out_data, задача интерфейса программного обеспечения Generate показывает предупреждение, что блоки водителя AXI4-потока IIO автоматически не произведены в модели интерфейса программного обеспечения. Можно либо вставить блоки драйверов из библиотеки пакетов поддержки встроенного кодера для целевой платформы в обозревателе библиотеки Simulink, либо повторно запустить рабочий процесс, сопоставив порты данных с векторными сигналами. Видеть, что программное обеспечение соединяет модель, у которой есть блоки водителя AXI4-потока IIO, вставленные в него, открытые hdlcoder_sfir_fixed_stream_sw. Модель использует блоки AXI4-Stream IIO Write (Embedded Coder Support Package for Xilinx Zynq Platform) и AXI4-Stream IIO Read (Embedded Coder Support Package for Xilinx Zynq Platform) для портов данных. Порты фильтра сопоставляются с AXI4-Lite блоками драйверов.

open_system('hdlcoder_sfir_fixed_stream_sw')

Сконфигурируйте модель со временем остановки inf. На вкладке Оборудование (Hardware) параметры оборудования, указанные в модели. Затем можно подключиться, построить и запустить приложение на целевой платформе для проверки основных функций HDL IP. См. раздел Начало работы с интерфейсом AXI4-Stream в рабочем процессе Zynq.