Консультант по рабочим процессам HDL проводит этапы создания кода HDL для подсистемы Simulink ® и процесса проектирования FPGA, такие как:

Проверка модели на совместимость генерации кода HDL и автоматическое исправление несовместимых настроек.

Создание кода HDL, тестового стенда и сценариев для создания и запуска кода и тестового стенда.

Создание испытательных стендов cosimulation или SystemVerilog DPI и покрытия кода (требуется Verifier™ HDL).

Синтез и анализ времени посредством интеграции со сторонними инструментами синтеза.

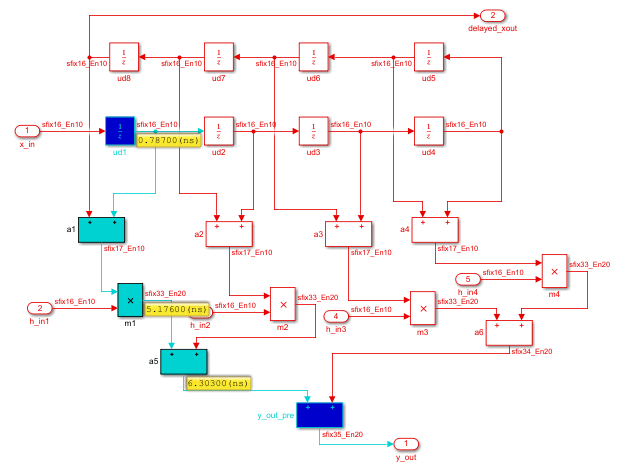

Обратная аннотация модели с информацией о критическом пути и другой информацией, полученной в процессе синтеза.

Завершите автоматизированные рабочие процессы для выбранных целевых устройств разработки FPGA, включая моделирование FPGA в цикле (требуется проверка HDL) и рабочий процесс ввода-вывода Simulink Real-Time™ FPGA.

В этом примере показано, как можно создать код HDL для модели фильтра FIR и синтезировать конструкцию на устройстве FPGA. Перед созданием кода HDL модель должна быть совместима для создания кода HDL. Сведения о проверке и обновлении модели на совместимость с HDL см. в разделе Проверка совместимости HDL модели Simulink с помощью помощника по коду HDL.

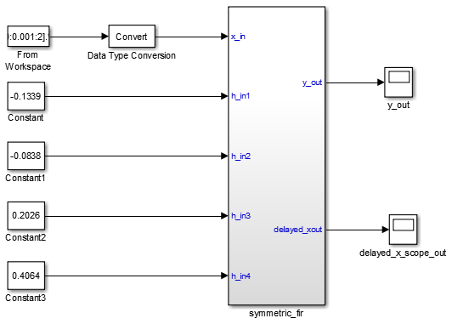

В этом примере используется модель симметричного фильтра FIR, совместимая с генерацией кода HDL. Чтобы открыть эту модель в командной строке, введите:

sfir_fixed

Модель использует разделение труда, которое подходит для конструирования ЛПВП.

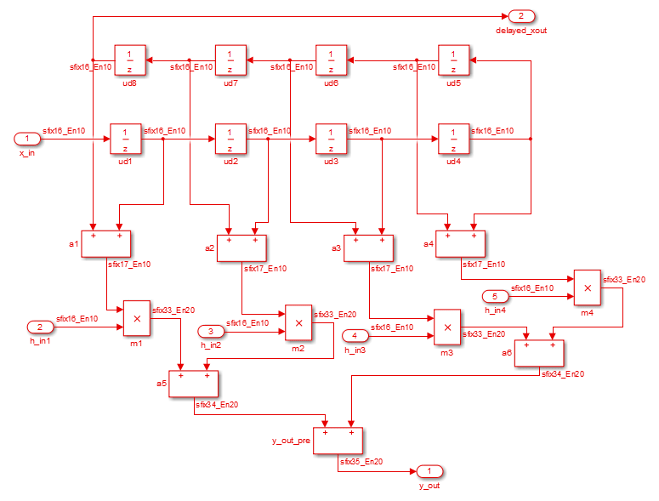

symmetric_fir подсистема, реализующая алгоритм фильтрации, является тестируемым устройством (DUT). Объект HDL генерируется из этой подсистемы.

Компоненты модели верхнего уровня, управляющие подсистемой, работают как испытательный стенд.

Модель верхнего уровня генерирует 16-разрядные входные сигналы с фиксированной точкой для symmetric_fir подсистема. Блок «Сигнал из рабочего пространства» генерирует тестовый входной (стимулирующий) сигнал для фильтра. Четыре постоянных блока обеспечивают коэффициенты фильтра. Блоки Scope используются для моделирования и не используются для генерации кода HDL.

Для перехода к symmetric_fir подсистема, введите:

open_system('sfir_fixed/symmetric_fir')

В MATLAB ®:

Создание папки с именем sl_hdlcoder_work, например:

mkdir C:\work\sl_hdlcoder_work

sl_hdlcoder_work хранит локальную копию модели примера и папок и сгенерированный код HDL. Используйте папку, которая не находится в дереве папок MATLAB.

Сделать sl_hdlcoder_work папка рабочая папка, например:

cd C:\work\sl_hdlcoder_workСохранение локальной копии sfir_fixed в текущую рабочую папку. Оставьте модель открытой.

Если не требуется синтезировать проект, но требуется создать код HDL, нет необходимости задавать траекторию движения инструмента. В помощнике по рабочим процессам HDL на шаге Задать цель > Задать целевое устройство и средство синтеза оставьте для инструмента синтеза значение по умолчанию No Synthesis Tool Specified, а затем запустите рабочий процесс.

Если требуется синтезировать проект на целевой платформе, прежде чем открыть помощник по рабочим процессам HDL и запустить рабочий процесс, настройте путь к инструменту синтеза. В этом примере используется Xilinx ® Vivado ®, поэтому необходимо установить Xilinx Vivado. Чтобы задать траекторию движения инструмента, используйте hdlsetuptoolpath для указания на установленный исполняемый файл Xilinx Vivado 2019.2. Дополнительно можно использовать другой выбранный инструмент синтеза и следовать этому примеру. Чтобы задать путь к этому инструменту синтеза, используйте hdlsetuptoolpath. Сведения о новейших поддерживаемых инструментах см. в разделах Языковая поддержка HDL и Поддерживаемые сторонние инструменты и оборудование.

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath',... 'C:\Xilinx\Vivado\2019.1\bin\vivado.bat');

Чтобы запустить помощник по рабочим процессам HDL из модели Simulink,

На вкладке Приложения выберите Кодер HDL. Появится вкладка Код HDL (HDL Code).

Выберите подсистему DUT в модели и убедитесь, что это имя подсистемы отображается в параметре Code for. Чтобы запомнить выбор, можно закрепить этот параметр. Щелкните Помощник по рабочим процессам (Workflow Advisor).

При открытии помощника по рабочим процессам HDL генератор кода может предупредить о несовместимости папки проекта. Чтобы открыть помощник, выберите Удалить slprj и продолжите.

На левой панели помощника по рабочим процессам HDL перечислены папки в иерархии. Каждая папка представляет группу или категорию связанных задач. На левой панели можно выбрать папку или отдельную задачу. Помощник по рабочим процессам HDL отображает информацию о выбранной папке или задаче на правой панели.

Чтобы узнать больше о каждой отдельной задаче, щелкните ее правой кнопкой мыши и выберите «Что это?».

![]()

Дополнительные сведения об окне помощника по рабочим процессам HDL см. в разделе Начало работы с консультантом по рабочим процессам HDL.

На шаге Set Target > Set Target Device and Synthesis Tool для инструмента Synthesis выберите Xilinx Vivado и выберите Запустить эту задачу.

Чтобы создать код, щелкните правой кнопкой мыши задачу «Создать код RTL» и «Тестирование» и выберите «Выполнить до выбранной задачи».

В окне FPGA Synthesis and Analysis (Синтез и анализ FPGA) > Perform Synthesis and P/R > Run Implementation (Выполнить синтез и анализ FPGA) снимите флажок Пропустить эту задачу и нажмите Apply (Применить).

Щелкните правой кнопкой мыши Аннотация модели с результатом синтеза (Annotate Model with Synthesis Result) и выберите Выполнить с выбранной задачей (Run to Selected Task).

Чтобы запустить рабочий процесс HDL в командной строке, можно экспортировать параметры помощника по рабочим процессам в сценарий. Для экспорта в сценарий в окне помощника по рабочим процессам HDL выберите «Файл» > «Экспорт в сценарий». В диалоговом окне «Экспорт конфигурации рабочего процесса» введите имя файла и сохраните сценарий.

Сценарий представляет собой файл MATLAB, который можно запустить из командной строки. Можно непосредственно изменить сценарий или импортировать сценарий в помощник по рабочим процессам HDL, изменить задачи и экспортировать обновленный сценарий. Дополнительные сведения см. в разделе Запуск рабочего процесса HDL со сценарием.