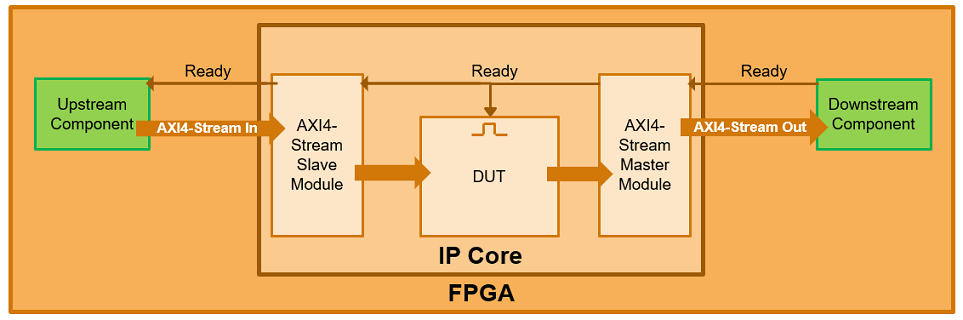

Программное обеспечение HDL Coder™ позволяет реализовать в модели упрощенный потоковый протокол. Программное обеспечение генерирует AXI4-Stream интерфейсы в ядре IP.

Чтобы сопоставить тестируемые порты (DUT) с AXI4-Stream интерфейсами, используйте упрощенный протокол AXI4-Stream. Не нужно моделировать фактический протокол AXI4-Stream и вместо этого можно использовать упрощенный протокол. При запуске IP Core Generation генерируемый код HDL содержит логику оболочки, которая преобразуется между упрощенным протоколом и фактическим протоколом AXI4-Stream. Упрощенный протокол требует меньше протокольных сигналов, облегчает механизм квитирования между действительными и готовыми сигналами и поддерживает пакеты произвольной длины.

Для операций записи и чтения используется упрощенный протокол AXI4-Stream. При необходимости создания интерфейса AXI4-Stream в ядре IP в интерфейсе DUT реализуются следующие сигналы:

Данные

Действительный

Дополнительно при сопоставлении скалярных портов DUT с интерфейсом AXI4-Stream можно моделировать следующие сигналы:

Готов

Другие протокольные сигналы, такие как:

TSRTB

TKEEP

TLAST

TID

TDEST

TUSER

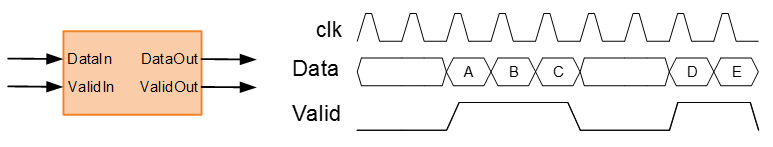

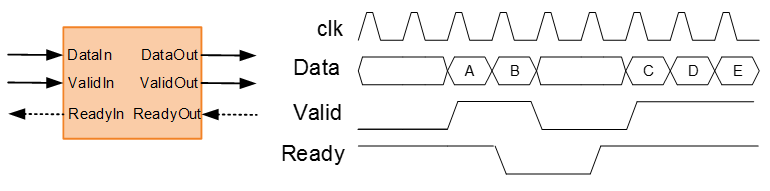

Когда сигнал Data является действительным, подается сигнал Valid. Эта диаграмма иллюстрирует отношение данных и действительного сигнала в соответствии с упрощенным протоколом потоковой передачи. При запуске процесса создания IP-ядра кодер HDL добавляет модуль потокового интерфейса в IP-ядро HDL, который преобразует упрощенный протокол в протокол полного AXI4-stream. На этой схеме тактовый сигнал представлен clk.

Если требуется смоделировать сигнал данных в виде потока выборок на границе DUT, выполните моделирование в режиме на основе выборок. В режиме на основе выборки можно моделировать сигнал данных как скаляр или вектор. При моделировании сигнала данных в виде вектора установите для параметра «Размер упаковки образца» значение «Все». В сгенерированном HDL коде векторные элементы упаковываются вместе, и весь вектор обрабатывается как один образец. Способ упаковки данных можно определить с помощью режима упаковки. См. раздел Размер упаковки образцов.

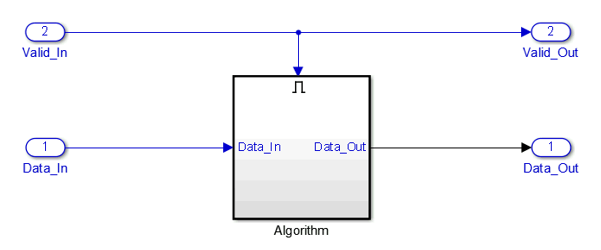

Заключите алгоритм, который обрабатывает сигнал данных с помощью включенной подсистемы.

Управление разрешенным портом включенной подсистемы осуществляется с помощью сигнала Valid.

Например, можно непосредственно подключить сигнал Valid к порту enable.

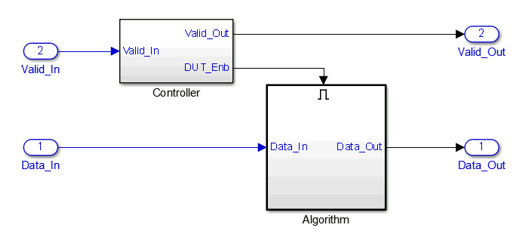

В DUT также можно использовать контроллер, который генерирует сигнал включения для включенной подсистемы.

Обратное давление используется нижестоящими компонентами, чтобы сообщить вышестоящим компонентам, что они не готовы к получению данных. Интерфейсы AXI4-Stream в DUT могут дополнительно включать сигнал Ready. Используйте сигнал Ready для:

Примените противодавление в AXI4-Stream подчиненном интерфейсе. Например, сбросьте сигнал Ready, когда нисходящий компонент не готов к приему данных.

Реагируйте на обратное давление в главном интерфейсе AXI4-Stream. Например, прекратите отправку данных, когда сигнал готовности компонента в нисходящем направлении мал.

При использовании одного канала потоковой передачи по умолчанию кодер HDL генерирует сигнал Ready и логику для обработки обратного давления. Логика обратного давления связывает сигнал Ready с сигналом DUT Enable. При низком уровне входного ведущего сигнала готовности DUT отключается, а выходной ведомый сигнал готовности приводится в действие на низком уровне. Поскольку кодер HDL генерирует логику обратного давления и сигнал Ready, при использовании одного канала потоковой передачи сигнал Ready является необязательным, и вам не нужно моделировать этот сигнал в порту DUT.

При использовании нескольких каналов потоковой передачи кодер HDL генерирует сигнал готовности и не генерирует логику обратного давления. В DUT с несколькими потоковыми каналами:

Главный канал игнорирует сигнал Ready от нисходящих компонентов.

Сигнал готовности подчиненного канала является высоким, что заставляет компоненты восходящего направления продолжать передачу данных.

Отсутствие логики обратного давления может привести к потере данных. Чтобы избежать потери данных и применить противодавление к ведомому интерфейсу или отреагировать на противодавление от главного интерфейса в вашей конструкции:

Смоделировать сигнал Ready для каждого дополнительного потокового интерфейса.

Сопоставьте смоделированный сигнал Ready с портом DUT для дополнительного интерфейса.

Если вы не моделируете сигнал Ready, задача Set Target Interface отображает предупреждение с именами интерфейсов, которым требуется порт Ready. Если проект не требует применения противодавления или реагирования на него, проигнорируйте это предупреждение.

При моделировании сигнала Ready в AXI4-Stream интерфейсах главный интерфейс игнорирует сигналы Data и Valid через один такт после отмены подтверждения сигнала Ready. После подачи сигнала готовности можно начать отправку сигналов Data и Valid. После отмены подтверждения сигнала Ready можно отправить еще один сигнал Data и Valid.

Если не моделировать сигнал готовности, кодер HDL генерирует сигнал и соответствующую логику обратного давления. Эта диаграмма иллюстрирует взаимосвязь между сигналами Data, Valid и Ready в соответствии с упрощенным протоколом потоковой передачи. При запуске процесса создания IP-ядра кодер HDL добавляет модуль потокового интерфейса в IP-ядро HDL, который преобразует упрощенный протокол в протокол полного AXI4-stream. На этой схеме тактовый сигнал представлен clk.

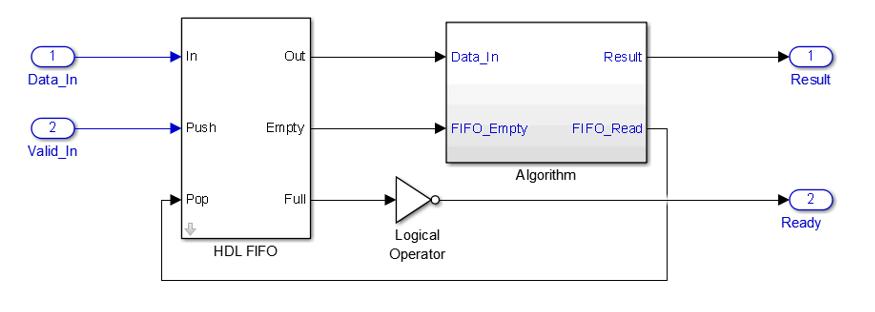

Например, если в DUT имеется First in first out (FIFO) для хранения кадра данных, для приложения противодавления к входному компоненту моделируйте сигнал Ready на основе сигнала FIFO Full.

Примечание

При включении балансировки задержки кодер вставляет одну или несколько задержек в сигнал Ready. Отключить балансировку задержки для тракта сигнала Ready.

При необходимости можно моделировать другие сигналы протокола AXI4-Stream. Если моделируются только требуемые сигналы Data и Valid, кодер генерирует сигналы протокола TREADY AND TLAST и AXI4-Stream.

Если не моделировать сигнал TLAST, кодер генерирует программируемый регистр в ядре IP, чтобы можно было указать размер пакета данных. Подробная информация о программируемом регистре размера пакета содержится в отчете о генерации IP-ядра.

Если требуется смоделировать сигнал данных в виде кадра на границе DUT, выполните моделирование в режиме на основе кадра. В основанном на кадрах режиме моделируйте сигнал данных как вектор и установите для параметра «Размер упаковки образца» значение «Нет». См. раздел Размер упаковки образцов.

Режим на основе кадров полезен для моделирования и моделирования взаимодействия системы между аппаратным и программным обеспечением и генерации кода для драйвера программного обеспечения.

При сопоставлении векторных портов с AXI4-Stream интерфейсами:

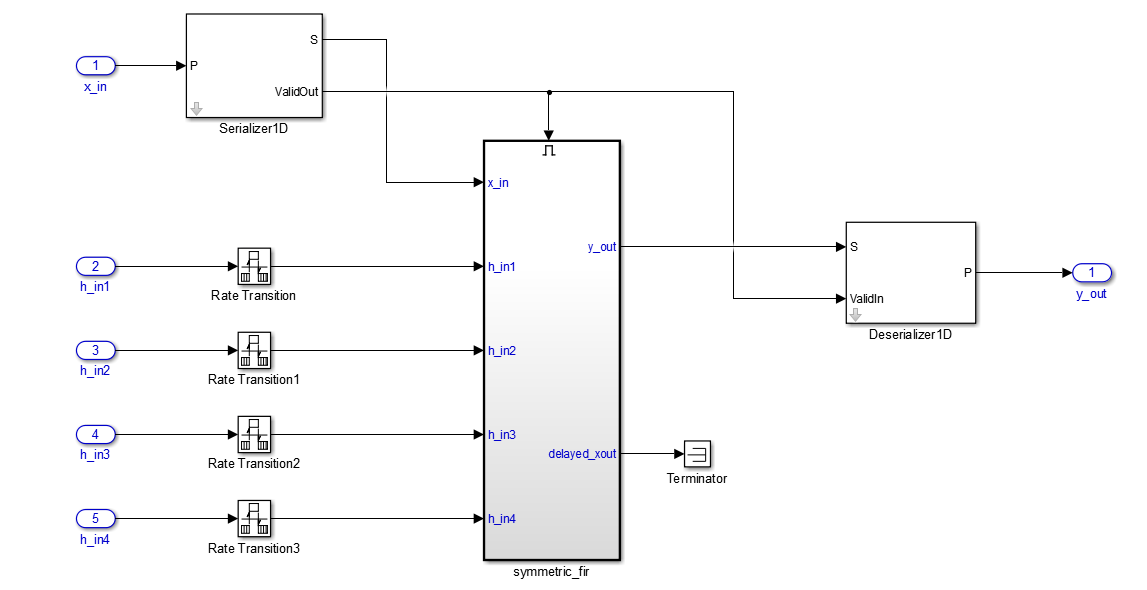

Подключите каждый порт входных векторных данных DUT к блоку Serializer1D.

Для блока Serializer1D должен быть установлен порт ValidOut, а для параметра Ratio - битовая ширина вектора.

Подключите каждый порт выходных векторных данных DUT к блоку Deserializer1D.

Для блока Deserializer1D должен быть установлен порт ValidIn, а для параметра Ratio - битовая ширина вектора.

Подключите каждый скалярный порт, который сопоставляется с интерфейсом AXI4-Lite, к блоку Rate Transition.

Коэффициент в блоке Rate Transition должен соответствовать коэффициенту в блоках Serializer1D и Deserializer1D.

Каждый скалярный порт, сопоставляемый с внешним портом, должен иметь то же время выборки, что и подсистема алгоритма потоковой передачи.

Подсистема алгоритма потоковой передачи соответствует тому же шаблону моделирования сигналов Data и Valid, что и шаблон для отображения скалярных портов на интерфейсы AXI4-Stream. См. раздел Данные модели и допустимые сигналы в Simulink.

Для отображения векторных портов на AXI4-Stream интерфейсы откройте hdlcoder_sfir_fixed_vector.slx модель. В hdlcoder_sfir_fixed_vector.slx symmetric_fir блок является подсистемой алгоритма потоковой передачи.

При запуске IP Core Generation технологический процесс, Вы можете нанести на карту несколько скалярные порты DUT к Рабским каналам Владельца и AXI4-потока AXI4-потока. Когда Вы используете векторные порты, Вы можете нанести на карту порты к самое большее одному каналу Владельца AXI4-потока и одному Рабскому каналу AXI4-потока.

Примечание

При использовании нескольких потоковых каналов кодер HDL генерирует сигнал Ready, но не генерирует логику обратного давления. Если вы хотите, чтобы ваша конструкция обрабатывала противодавление, смоделируйте сигнал Ready в вашей конструкции.

Дополнительные сведения см. в разделе Создание IP-ядра HDL с несколькими AXI4-Stream и основными интерфейсами AXI4.

При запуске рабочего процесса генерации IP Core используйте программное обеспечение HDL Coder для проектов с несколькими частотами выборки. При сопоставлении портов интерфейса с интерфейсами AXI4-Stream Master или AXI4-Stream Slave для использования нескольких скоростей дискретизации сопоставьте порты DUT, которые сопоставляются с этими интерфейсами AXI4, для выполнения с самой высокой скоростью проектирования или с более низкой скоростью, чем скорость проектирования.

Кодер HDL запускает порты DUT, сопоставленные с AXI4-Stream главным и подчиненным интерфейсами, со скоростями медленнее, чем скорость проектирования модели:

Установка действительного сигнала ведущего канала AXI4-Stream на высокий уровень в первом цикле каждые N тактов. Например, если расчетная скорость в восемь раз выше, чем скорость портов DUT, действительный сигнал является высоким для первого тактового цикла каждые восемь тактовых циклов.

Установка противодавления на AXI4-Stream подчиненном интерфейсе для обеспечения потоковой передачи входящих данных со скоростью одного кадра данных каждые N тактов. Например, если расчетная скорость в восемь раз выше, чем у портов DUT с медленной скоростью, первый кадр передается в потоке в такт первого, второй кадр в такт девятого и так далее.

При сопоставлении порта DUT AXI4-Stream Interface с самой высокой скоростью в конструкции действительный сигнал всегда является высоким, что гарантирует отсутствие обратного давления на подчиненном интерфейсе AXI4-Stream.

Проектируя модели, у которых есть несколько частот дискретизации, нанесенные на карту порты интерфейса владельца всего AXI4-потока DUT должны бежать по тому же уровню. Все порты DUT подчиненного интерфейса AXI4-Stream должны работать с одинаковой скоростью.

Дополнительные сведения см. в разделе Создание многоскоростного ядра IP.

При выполнении рабочего процесса создания IP-ядра для модели, содержащей векторные данные, можно указать, как векторные данные обрабатываются как образец или как кадр, используя измерение упаковки образцов. Если векторные данные обрабатываются как образец, можно указать способ упаковки векторных элементов с помощью опции Режим упаковки (Packing mode).

Укажите, обрабатываются ли векторные данные как образец или как кадр.

Ничего. Это значение по умолчанию. Если задано значение Нет (None), векторы обрабатываются как кадры, а векторные элементы передаются один за другим. Например, когда вход является вектором шесть к одному в первом такте, первый векторный элемент передается в поток, второй векторный элемент - во втором такте и так далее. Модель должна содержать блок Serializer для входных данных и блок Deserializer для выходных данных, чтобы использовать этот режим. Режим упаковки недоступен, если для параметра «Размер упаковки образца» установлено значение «Нет».

Все. При указании «Все» векторы упаковываются вместе и передаются в виде потока за один тактовый цикл. Например, когда входной сигнал представляет собой вектор «шесть к одному», все векторные элементы упаковываются вместе и передаются потоком в одном такте. В этом случае можно указать способ упаковки векторных элементов с помощью опции Режим упаковки (Packing mode).

Укажите способ упаковки векторных элементов, если для параметра «Размер упаковки образца» задано значение «Все». Режим упаковки применяется к AXI4-Stream ведомому и ведущему каналам. На ведущем канале данные упаковываются с использованием форматов Bit Aligned или Power of 2 Aligned. На подчиненном канале данные распаковываются на основе формата упаковки ведущего канала.

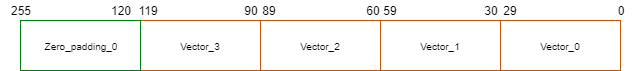

Выровнен по битам. В этом режиме векторные элементы упаковываются непосредственно рядом друг с другом. Если ширина упакованного бита меньше ширины AXI4-Stream канала, то упакованные данные заполняются нулями для соответствия ширине канала.

Например:

Ширина AXI4-речного-русла составляет 256 битов.

Векторы имеют длину 30 бит и 4 векторных кадра. Общая ширина данных составляет 120 бит.

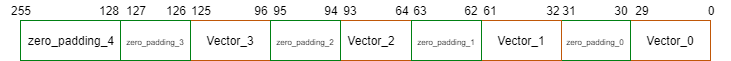

Если установлен режим упаковки Bit Aligned, данные AXI4-Stream упаковываются, как показано на этой схеме

Мощность 2 выровненных. В этом режиме векторные элементы сначала заполняются нулями до ближайшей степени двух границ. Затем заполненные элементы упаковывают вместе. Если битовая ширина упакованного вектора меньше AXI4-Stream ширины канала, то упакованные данные заполняются нулями для соответствия ширине канала.

Например:

Ширина AXI4-речного-русла составляет 256 битов.

Векторы имеют длину 30 бит и 4 векторных кадра. Общая ширина данных составляет 120 бит.

Если для режима упаковки установлено значение Power of 2 Aligned, AXI4-Stream данные упаковываются, как показано на следующей схеме:

Каждый векторный элемент битовой ширины 30 дополнен нулями битовой ширины 2 для расширения его до 32, ближайшей степени двух границ.

При сопоставлении скалярных или векторных портов DUT с AXI4-Stream интерфейсами:

Xilinx ® Zynq ® -7000 или Intel ® Quartus ® Prime должны быть целевой платформой.

Xilinx Vivado ® или Intel Quartus Prime должны быть вашим инструментом синтеза.

Синхронизация процессора/FPGA должна быть свободной.

При использовании кадрового моделирования нельзя использовать сигналы протокола, отличные от сигналов Data и Valid. Например, Ready и TLAST не поддерживаются.