Используйте оптимизации площади и скорости в Coder™ HDL, чтобы сэкономить ресурсы и улучшить время проектирования на целевом устройстве FPGA. Эти оптимизации не изменяют функционального поведения алгоритма, но могут оптимизировать определенные ресурсы в проекте, ввести задержку или вызвать разницу в частоте выборки.

Первоначально можно генерировать код HDL и синтезировать дизайн на платформе FPGA без оптимизации. Если проект не соответствует требованиям к времени, можно включить оптимизации и повторно запустить рабочий процесс до тех пор, пока проект не будет соответствовать требованиям к площади и скорости. См. раздел Основной рабочий процесс создания кода HDL.

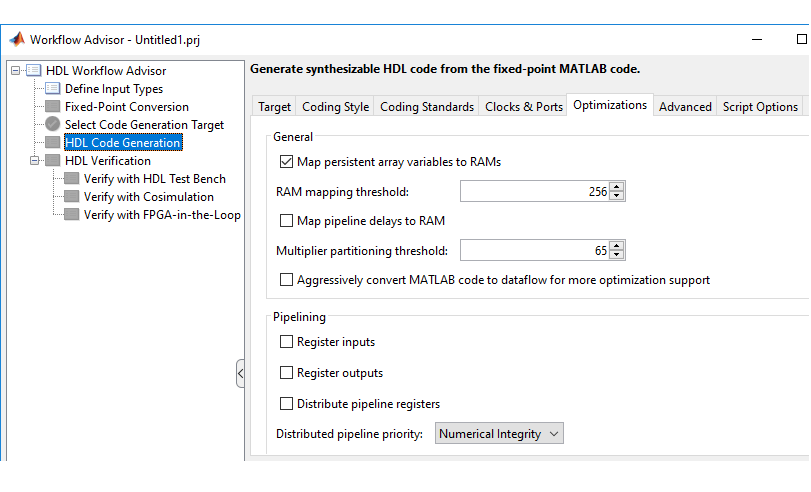

Чтобы включить оптимизацию кода MATLAB ®, откройте мастер Workflow Advisor из MATLAB. В Advisor в задаче Создание кода HDL включите параметры на вкладке Оптимизация.

Можно включить оптимизацию на уровне модели и на уровне блока. Укажите оптимизации на уровне модели:

В диалоговом окне «Параметры конфигурации» на панели «Создание кода HDL» > «Оптимизация». См. Панель создания кода HDL: Оптимизация.

В командной строке с помощью makehdl или hdlset_param для установки значения свойства.

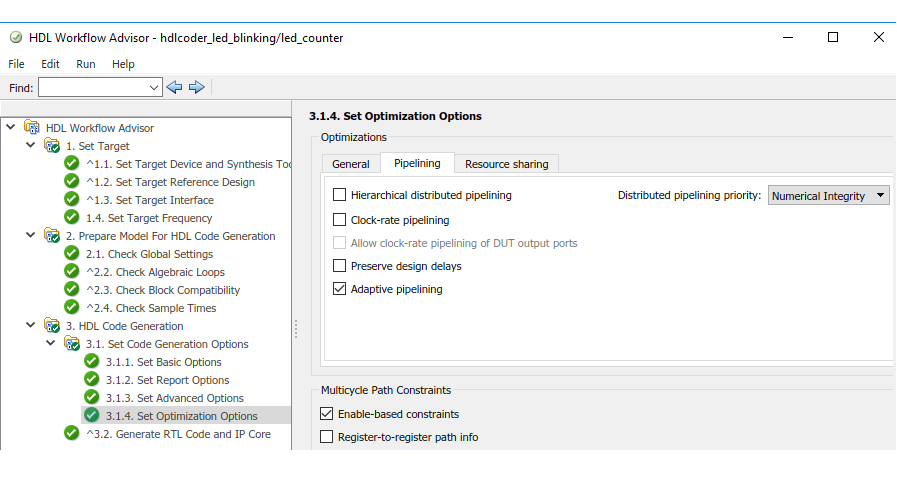

В помощнике Simulink ® HDL Workflow Advisor выберите задание Задать параметры генерации кода > Задать параметры оптимизации.

Подсистемы модели наследуют параметры оптимизации на уровне модели. Можно изменить настройки уровня подсистемы в диалоговом окне «Свойства блока HDL» для подсистем или с помощью hdlset_param функция. Можно также задать определенные дополнительные настройки для определенных блоков в модели, такие как добавление трубопроводов на входе и выходе. Эта таблица иллюстрирует различные оптимизации, доступные на уровне блока и на уровне модели.

| Оптимизация | Уровень модели? | Уровень подсистемы? | Комментарии |

|---|---|---|---|

| Балансировка задержки | Да | Да | – |

| Отображение ОЗУ | Да | Нет | – |

| Адаптивная конвейерная обработка | Да | Да | – |

| Конвейеризация тактовой частоты | Да | Да | – |

| Распределенная конвейерная обработка | Да | Да | На уровне модели используется иерархическая распределенная конвейерная обработка. Для применения оптимизации в иерархиях подсистем включите распределенную конвейерную обработку на каждом уровне подсистем. |

| Совместное использование ресурсов | Да | Да | На уровне модели указывается тип ресурсов, которыми требуется поделиться, например, сумматоры и множители. На уровне блока задается SharingFactor. |

| Вытекание | Нет | Да | – |

Чтобы увидеть эффект оптимизации, выполните следующие действия.

Можно создать отчет по оптимизации с кодом HDL. Сведения о том, как включить этот отчет, см. в разделе Создание и использование отчетов о создании кода.

Откройте созданную модель или создайте модель проверки. Созданная модель является поведенческой моделью кода HDL, которая показывает эффект реализации блоков и оптимизации, которые были включены. Чтобы проверить номера созданной модели с исходной моделью, можно создать модель проверки. См. Сгенерированная модель и модель проверки.

Совет

Чтобы эффективно использовать оптимизации, измените настройку времени образца для постоянных блоков с Inf кому -1.

Модель может иметь задержки проектирования и задержки трубопровода. Задержки проектирования - это задержки, которые добавляются в модель вручную. Задержки конвейера - это задержки, которые вводятся параметрами конвейерной обработки, заданными в блоках, реализациями блоков, такими как метод Ньютона-Рафсона, собственные операторы с плавающей запятой или оптимизацией скорости. Эти задержки отображаются в сгенерированном коде HDL, сгенерированной модели и модели проверки.

Общие параметры оптимизации включают в себя:

Отображение ОЗУ: используйте параметры отображения ОЗУ для отображения больших задержек, постоянных переменных в коде MATLAB и задержек конвейера в ОЗУ на основе ширины порогового бита. См. также Сопоставление RAM для кода MATLAB и Параметры сопоставления RAM.

Балансировка задержки: Включена по умолчанию, эта оптимизация уравновешивает задержки конвейера, вставляя соответствующие задержки в параллельные пути. Оптимизация сопоставляет числа созданной модели с исходной моделью. Эффект этой оптимизации можно увидеть в разделе Балансировка задержки отчета по оптимизации. См. раздел Балансировка задержки.

Оптимизация скорости улучшает время проектирования на целевом FPGA за счет оптимизации критического пути. Чтобы определить критический путь, можно запустить Generic ASIC/FPGA workflow-процесс для устройства FPGA, а затем аннотирование критического пути или использование отчетов синхронизации.

Для более быстрой идентификации критического пути и ускорения итеративного процесса поиска и оптимизации критического пути используйте оценку критического пути. Нет необходимости выполнять синтез или генерировать код HDL. Оценка критического тракта использует статический анализ синхронизации с данными синхронизации из целевых баз данных синхронизации. Эффект этой оптимизации можно увидеть в разделе Оценка критического пути отчета по оптимизации. См. раздел Оценка критического пути без выполнения синтеза.

Оптимизация скорости включает в себя:

Конвейер тактовой частоты: оптимизация Simulink, которая включена по умолчанию, и запускает регистры конвейера с более высокой тактовой частотой, когда вы указываете коэффициент избыточной дискретизации больше единицы. Для удаления иерархических границ в подсистеме используйте конвейер тактовой частоты с выравниванием иерархии, тем самым улучшая ресинхронизацию. См. раздел Конвейеризация тактовой частоты.

Распределенная конвейерная обработка - оптимизация, которая повторно регистрирует существующие задержки или задается с помощью параметров блока InputPipeline и OutputPipeline. Чтобы сохранить существующие задержки, включите параметр Сохранить задержки проектирования. Включение иерархической распределенной конвейерной обработки в модели и распределенной конвейерной обработки в подсистемах для ресинхронизации регистров по иерархиям. Эффект этой оптимизации можно увидеть в разделе «Распределенная конвейерная обработка» отчета по оптимизации. См. Распределенная конвейерная обработка и иерархическая распределенная конвейерная обработка.

Адаптивная конвейеризация: оптимизация Simulink, которая вставляет регистры конвейера на входе или выходе или оба порта определенных блоков для создания шаблонов, которые эффективно отображают блоки в блоки DSP на целевом устройстве FPGA. Оптимизация учитывает целевое устройство, целевую частоту, длину слова множителя и параметры свойства блока HDL. Эффект этой оптимизации можно увидеть в разделе «Адаптивная конвейерная обработка» отчета об оптимизации. См. раздел Адаптивное конвейерирование.

Разворачивание цикла: оптимизация MATLAB, которая разворачивает цикл путем создания нескольких экземпляров тела цикла в сгенерированном коде. Можно также частично развернуть цикл. См. раздел Оптимизация контуров MATLAB

Оптимизация площадей сокращает использование ресурсов проекта. Оптимизация проекта для области может снизить скорость, с которой проект работает на FPGA.

Оптимизация площадей включает в себя:

Совместное использование ресурсов - оптимизация, которая идентифицирует несколько функционально эквивалентных ресурсов и заменяет их одним ресурсом. На уровне модели указываются ресурсы, которые требуется использовать совместно, такие как сумматоры и множители. На уровне подсистемы указывается SharingFactor в зависимости от количества совместно используемых ресурсов в проекте. Используя оптимизацию с конвейерированием тактовой частоты, можно указать способ оверклокинга общих ресурсов. См. раздел Совместное использование ресурсов

Потоковая передача: оптимизация Simulink, которая разбивает векторный путь данных на несколько меньших векторных путей данных на основе параметра StreamingFactor, заданного в подсистемах, тем самым снижая потребление аппаратных ресурсов. См. раздел Потоковая передача.

Loop Streaming: оптимизация MATLAB, которая выполняет потоковую передачу цикла путем создания экземпляра тела цикла один раз и использования этого экземпляра для каждой итерации цикла. Генератор кода выполняет избыточную выборку экземпляра тела цикла, чтобы сохранить функциональный эквивалент сгенерированного цикла исходному циклу. См. раздел Оптимизация контуров MATLAB