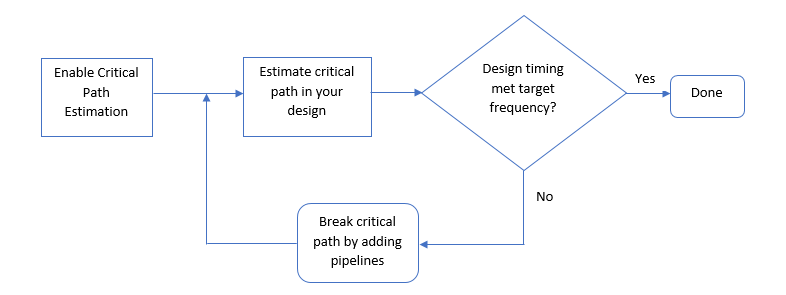

Критический путь - это комбинированный путь между входом и выходом, который имеет максимальную задержку. Используйте программное обеспечение HDL Coder™ для поиска критического пути в конструкции. Чтобы синхронизация критического тракта соответствовала целевой частоте, которую должна достичь конструкция, разорвать критический путь путем добавления задержек. Дополнительные задержки увеличивают задержку и увеличивают использование регистра в целевом FPGA.

Чтобы быстро определить наиболее вероятный критический путь в конструкции, используйте оценку критического пути. При оценке критического пути нет необходимости выполнять синтез или генерировать код HDL. Оценка критического пути ускоряет этот итеративный процесс поиска критического пути и последующей оптимизации критического пути до тех пор, пока время проектирования не достигнет желаемой частоты.

Оценка критического пути без использования инструментов синтеза может привести к неточным результатам синхронизации. Оценка критического пути предназначена для ускорения процесса итерации конструкции. Оценка критического пути является альтернативой аннотированию критического пути путем выполнения синтеза и анализа FPGA с помощью консультанта по рабочим процессам HDL.

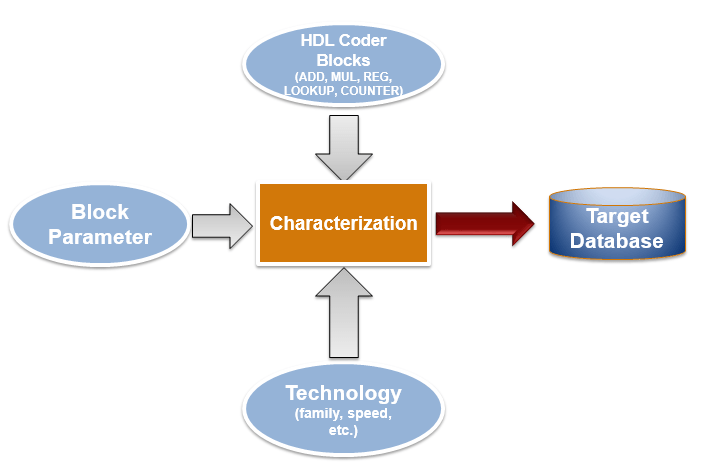

Кодер HDL находит оцененный критический тракт путем выполнения статического анализа синхронизации с данными синхронизации из целевых баз данных синхронизации. Создание баз данных синхронизации для указанного семейства оконечных устройств, класса скорости оконечного устройства и целевого инструмента с помощью genhdltdb функция. По умолчанию кодер HDL имеет базы данных синхронизации для следующих целевых устройств:

Циклон V Altera ®

Intel ® Stratix V

Xilinx ® Artix ® -7, класс скорости -1

Xilinx Kintex ® -7, класс скорости -1

Kilinx Kintex UltraScale™, класс скорости -1

Xilinx Virtex ® -4, класс скорости -10

Virtex-7 Xilinx, класс скорости -1

Xilinx Zynq ®, класс скорости -1

Xilinx Zynq UltraScale+™, класс скорости -1

Для создания баз данных синхронизации HDL Coder характеризует основные компоненты проектирования, такие как блоки Simulink ®, блочные архитектуры и подкомпоненты этих блоков, для конкретных целевых устройств.

Генератор кода анализирует конструкцию модели, чтобы разложить ее на блоки и подкомпоненты в базах данных синхронизации. Если конструкция состоит из блоков или подкомпонентов в базах данных синхронизации, генератор кода может оценить критический путь синхронизации более точно. Если в проекте используются компоненты, отсутствующие в базах данных синхронизации, создается отдельный сценарий выделения для отображения нехарактерных блоков. Если данные синхронизации являются неполными для частей конструкции, возможно, что расчетный критический путь не соответствует фактическому критическому пути.

Если оконечное оборудование является одним из оконечных устройств, поддерживаемых для оценки критического тракта, то количество таймирования и оцененный критический тракт являются более точными. Если оконечное оборудование не является поддерживаемым устройством или не входит в одно и то же семейство устройств, можно оценить критический путь, но возможно, что номера синхронизации не являются точными.

Критический путь для проекта можно оценить в диалоговом окне «Параметры конфигурации» или в командной строке. Чтобы оценить критический путь в диалоговом окне Параметры конфигурации (Configuration Parameters):

Создание отчета об оценке критического пути.

На вкладке Приложения выберите Кодер HDL. Появится вкладка Код HDL (HDL Code).

Выберите Settings (Настройки) > Report Options (Параметры отчета), а затем выберите Generate high-level timing critical path report (Генерировать высокоуровневый

Отключите генерацию кода HDL для модели. На вкладке Создание кода HDL > Глобальные параметры настройки > Дополнительно снимите флажок Генерировать код HDL.

Для оценки критического пути в проекте не требуется запускать полный процесс создания кода. При отключении генерации кода HDL процесс выполняется до тех пор, пока кодер HDL не создаст созданную модель и не отобразит сценарий оценки критического пути. Вы избегаете выполнения большей части процесса создания кода, что экономит время на оценку критического пути, особенно для больших моделей.

Если конструкция содержит типы данных с плавающей запятой, включите Native Floating Point режим. В диалоговом окне «Параметры конфигурации» на панели «Создание кода HDL» > «Плавающая точка» задайте для параметра «Библиотека IP с плавающей точкой» значение Native Floating Point.

Задайте путь к сгенерированным базам данных синхронизации для целевого устройства. В диалоговом окне Configuration Parameters (Параметры конфигурации) на панели HDL Code Generation (Создание кода HDL) > Report (Отчет) выберите параметр Generate high-level timing critical path report (Генерировать высокоуровневый отчет о критическом пути синхронизации), а затем задайте путь к создаваемым базам данных синхронизации, щелкнув Browse (Обзор) и выбрав целевую папку.

По умолчанию в целевой папке отображаются некоторые из сохраненных каталогов базы данных синхронизации на основе целевой конфигурации. Если поле Custom Timing Database Directory пусто или целевая конфигурация не имеет баз данных синхронизации, по умолчанию кодер HDL использует базы данных синхронизации для устройства Xilinx Artix-7, speed grade -1 для генерации отчета об оценке критического пути.

Создание отчета об оценке критического пути. На панели Создание кода HDL (HDL Code Generation) щелкните Применить (Apply), а затем Создать (Generate).

Кодер HDL генерирует отчет об оценке критического пути и отображает в окне команд MATLAB ® сообщения, содержащие ссылку на сценарий выделения и сценарий, очищающий выделение.

Этот код используется для создания сценария рабочего процесса или отчета в командной строке. Укажите modelname и dutname переменные, основанные на конструкции, для которой требуется оценить критический путь. Задайте путь к сгенерированным базам данных синхронизации для целевого устройства с помощью hdlset_param функция. Если включить создание отчета об оценке критического пути и не задать путь к базе данных синхронизации для целевого устройства, кодер HDL выполняет поиск баз данных синхронизации по умолчанию для указанного семейства целевых устройств и уровня скорости целевого устройства. Если базы данных синхронизации для указанного целевого устройства недоступны, по умолчанию кодер HDL использует базы данных синхронизации для устройства Xilinx Artix-7, speed grade -1 для генерации отчета оценки критического пути. В этом примере используется sfir_single модель.

% Specify model and subsystem names modelname = 'sfir_single'; dutname = 'sfir_single/symmetric_fir'; open_system(modelname) % Disable HDL code generation for faster generation % of critical path estimation report hdlset_param(modelname,'CriticalPathEstimation','on'); hdlset_param(modelname,'GenerateHDLCode','off'); % If design contains single data types, % enable native floating-point support fpconfig = hdlcoder.createFloatingPointTargetConfig('NativeFloatingPoint'); hdlset_param(modelname,'FloatingPointTargetConfig',fpconfig); % Set path of generated timing databases for target device hdlset_param(modelname,'TimingDatabaseDirectory','C:\Work\Database'); % Generate report makehdl(dutname)

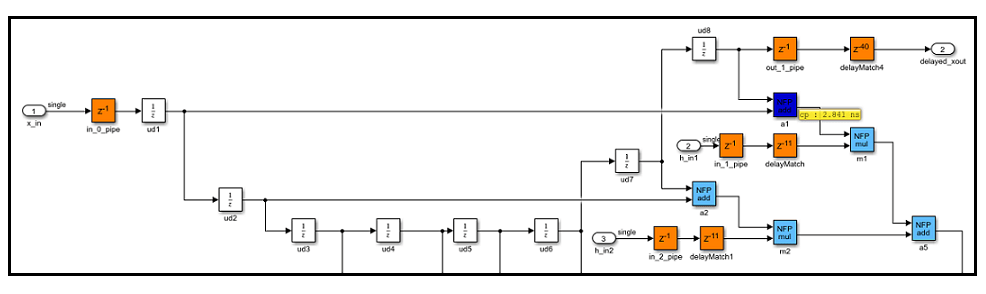

При щелчке по ссылке на criticalpathestimated сценарий, генератор кода выделяет критический путь в созданной модели. В созданной модели отображается информация о синхронизации критического тракта и блоки, находящиеся на этом тракте. На этом рисунке показан раздел модели Simulink с аннотированным критическим путем. Собственные операторы с плавающей запятой выделены светло-синим цветом, а задержки - оранжевым. Блок, являющийся частью критического контура, подсвечивается темно-синим цветом, а значение критического контура аннотируется рядом с блоком. Дополнительные сведения о различных цветах см. в разделах Сгенерированная модель и модель проверки.

Чтобы снять выделение, щелкните ссылку на clearhighlighting сценарий.

Чтобы оптимизировать критический путь, разорвите критический путь, добавив регистры трубопровода. Если используется Native Floating Point, задайте для LatencyStrategy значение Max для улучшения сроков. Повторно создайте отчет об оценке критического пути и сценарий, выделяющий критический путь в проекте. Этот процесс можно повторить до тех пор, пока время проектирования не достигнет требуемой частоты.

В этой таблице показаны блоки, для которых характерны собственные типы с фиксированной и одинарной точностью с плавающей запятой. Эти блоки являются частью базы данных синхронизации для каждого поддерживаемого целевого устройства.

Математические операции

| Блоки симулятора | Фиксированная точка | Одиночная (собственная плавающая точка) |

|---|---|---|

| Брюшной пресс | ✓ | ✓ |

| Добавить | ✓ (Блок не может иметь более двух входов) | ✓ |

| Вычесть | ✓ | ✓ |

| Продукт | ✓ | ✓ |

| Выгода | ✓ | ✓ |

| Разделиться | ✓ | ✓ |

| ЛПВП взаимный | ✓ | ✓ |

| Функция округления | ✓ | ✓ |

| Унарный минус | ✓ | ✓ |

| Знак | ✓ | ✓ |

| Измениться | ✓ | ✓ |

| Комплекс для реального Imag | ✓ | ✓ |

Математические функции

Тригонометрические функции

Экспонента/Логарифм/Мощность

| Блоки симулятора | Фиксированная точка | Одиночная (собственная плавающая точка) |

|---|---|---|

| Exp | - | ✓ |

| Получение мощности двух | - | ✓ |

| Pow10 | - | ✓ |

| Регистрация | - | ✓ |

| Log10 | - | ✓ |

Преобразования и сравнения

| Блоки симулятора | Фиксированная точка | Одиночная (собственная плавающая точка) |

|---|---|---|

| Преобразование типа данных | ✓ | ✓ |

| Поплавковый тип | - | ✓ |

| Реляционный оператор | ✓ | ✓ |

| Сравнить с константой | ✓ | ✓ |

| MinMax | ✓ | ✓ |

Логические и битовые операции

| Блоки симулятора | Фиксированная точка | Одиночная (собственная плавающая точка) |

|---|---|---|

| Битовый конкат | ✓ | - |

| Извлечь биты | ✓ | - |

| Битовый сдвиг | ✓ | - |

| Битовый срез | ✓ | - |

| Побитовый оператор | ✓ | - |

| Логический оператор | ✓ | ✓ |

Задержки и маршрутизация сигналов

| Блоки симулятора | Фиксированная точка | Одиночная (собственная плавающая точка) |

|---|---|---|

| Единичная задержка | ✓ | ✓ |

| Задержка | ✓ | ✓ |

| Автор шины | ✓ | ✓ |

| Селектор шины | ✓ | ✓ |

| Demux | ✓ | ✓ |

| Мультипортовый коммутатор | ✓ | ✓ |

| Отборщик | ✓ | ✓ |

| Выключатель | ✓ | ✓ |

Операции HDL и RAM HDL

| Блоки симулятора | Фиксированная точка | Одиночная (собственная плавающая точка) |

|---|---|---|

| Счетчик свободно работает | ✓ | ✓ |

| Счетчик ограничен | ✓ | ✓ |

| Счетчик HDL | ✓ | ✓ |

| Двухпортовая ОЗУ | ✓ | ✓ |

| Двухскоростная двухпортовая ОЗУ | ✓ | ✓ |

| Простая двухпортовая оперативная память | ✓ | ✓ |

| Однопортовая ОЗУ | ✓ | ✓ |

| Deserializer1D | ✓ | ✓ |

| Serializer1D | ✓ | ✓ |

Атрибуты сигнала и таблицы подстановки

| Блоки симулятора | Фиксированная точка | Одиночная (собственная плавающая точка) |

|---|---|---|

| Постоянный | ✓ | ✓ |

| 1-D Таблица подстановки | ✓ | ✓ |

| 2-D Таблица подстановки | ✓ | ✓ |

| n-D таблица подстановки | ✓ | ✓ |

| Переход ставки | ✓ | ✓ |

| Преобразование сигналов | ✓ | ✓ |

| Спецификация сигнала | ✓ | ✓ |

Пользовательские функции

| Блоки симулятора | Фиксированная точка | Одиночная (собственная плавающая точка) |

|---|---|---|

| Функция MATLAB | - | ✓ |

При использовании функциональных блоков MATLAB и создании кода с помощью MATLAB Datapath архитектура, кодер HDL преобразует алгоритм MATLAB в блок-схему Simulink. В созданной модели оценка критического пути может аннотировать критический путь внутри MATLAB Function блок и поперек MATLAB Function граница блока с другими блоками Simulink. См. также раздел Оптимизация HDL по границе функционального блока MATLAB с использованием архитектуры Datapath MATLAB.

Оценка критического пути не учитывает информацию о стробировании тактового сигнала для различных последовательных элементов в вашей конструкции.

Если модель содержит несколько скоростей выборки или использует оптимизации скорости и площади, которые вставляют регистры трубопровода, конструкция становится многоскоростной и может иметь многоцикловые пути. Для многоскоростных моделей оценка критического пути позволяет обрабатывать медленные и быстрые пути передачи данных с одинаковой скоростью. Путь данных, который имеет более высокую тактовую частоту, может быть выделен как критический путь, когда проект имеет другой путь данных с более низкой скоростью. Это может привести к тому, что оценка критического пути сообщит неточные результаты синхронизации.

Чтобы проверить предполагаемую информацию о критическом пути, откройте помощник по рабочим процессам HDL и запустите Generic ASIC/FPGA рабочий процесс для целевого устройства в модель Annotate с задачей результата синтеза.

Если есть single типы данных в вашей конструкции и вы используете Native Floating Point иногда сценарий оценки критического пути выделяет один оператор с плавающей запятой в создаваемой модели. Генератор кода выделяет один блок, поскольку алгоритмы с плавающей запятой требуют больших вычислений, а критический путь может быть внутренним путем от регистра к регистру в операторе с плавающей запятой.

В этом случае для оптимизации синхронизации критического тракта установите для LatencyStrategy значение Max для блока Simulink, соответствующего этому оператору.

Кроме того, оценка критического пути с собственной плавающей запятой не поддерживается для блоков со значением LatencyStategy Custom.

При включении оценки критического пути возможно, что сгенерированный код HDL отличается от отчета для блока задержки, имеющего внешний сброс или разрешающий порт. Кроме того, для таких блоков, как MinMax, количество созданных HDL-файлов может отличаться при включении оценки критического пути. Это изменение происходит из-за определенных оптимизаций, выполняемых генератором кода при включении этой оптимизации. Оптимизация изменяет только способ отображения кода и не влияет на функциональность.

Ниже приведены блоки Simulink, для которых сгенерированный код HDL потенциально может отличаться.

Блок задержки, имеющий внешний порт сброса или включения

MinMax

Единичная задержка включена синхронно

Единичная задержка, сбрасываемая синхронно

Единичная задержка Включена Сбрасываемая Синхронная

Включенная задержка

Сбрасываемая задержка

Задержка с отводом

Дискретный фильтр FIR

Биквадский фильтр

Функция MATLAB

Оценка критического пути пытается учесть задержку маршрутизации, используя коэффициент оценки. Без текущего места и маршрута трудно точно учесть задержку маршрутизации.

Кодер HDL выводит нехарактерные блоки, которые по своей природе являются комбинационными блоками с нулевой задержкой. Генератор кода обрабатывает другие блоки как регистры.

Если целевое устройство не имеет характеристик синхронизации, аналогичных одному из поддерживаемых целевых устройств, оценка критического пути не может точно вычислить критический путь.

genhdltdb | hdlcoder.FloatingPointTargetConfig | makehdl