Когда Вы управляете универсальным IP Основным технологическим процессом Поколения для своей модели Simulink® или нацелены на Ваш собственный справочный дизайн, который Вы создали, Вы можете произвести IP ядро HDL с несколькими интерфейсами AXI4-потока, интерфейсами Видео AXI4-потока или Основными интерфейсами AXI4. Сведения об этих интерфейсах см. в разделе Интерфейсы целевой платформы.

Можно использовать несколько потоковых интерфейсов для упрощения высокоскоростной передачи данных в различных приложениях, таких как:

Передача данных между АЦП и АЦП

Программно-определяемые алгоритмы радиосвязи, обрабатывающие несколько каналов приемопередатчика

Алгоритмы визуализации, выполняющие аннотацию изображения или обнаружение объекта

Определить больше чем один AXI4-поток, Видео AXI4-потока или Основной канал AXI4:

В задании Set Target Device and Synthesis Tool выберите IP Core Generation в качестве целевого рабочего процесса и Generic Xilinx Platform или Generic Altera Platform в качестве целевой платформы. Запустите эту задачу.

Чтобы добавить несколько целевых интерфейсов, в задаче Set Target Interface в разделе Target Platform Interfaces таблицы Target platform interface выберите Add more....

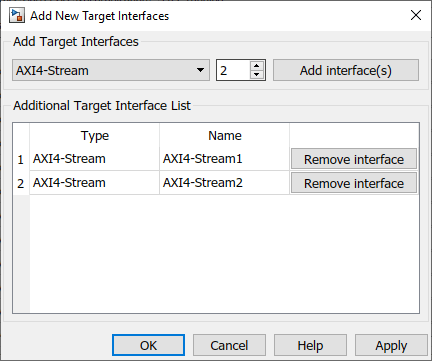

Затем можно добавить дополнительные интерфейсы в диалоговом окне Добавить новые целевые интерфейсы (Add New Target Interfaces). Укажите тип добавляемого интерфейса, количество интерфейсов и пользовательское имя для каждого дополнительного интерфейса.

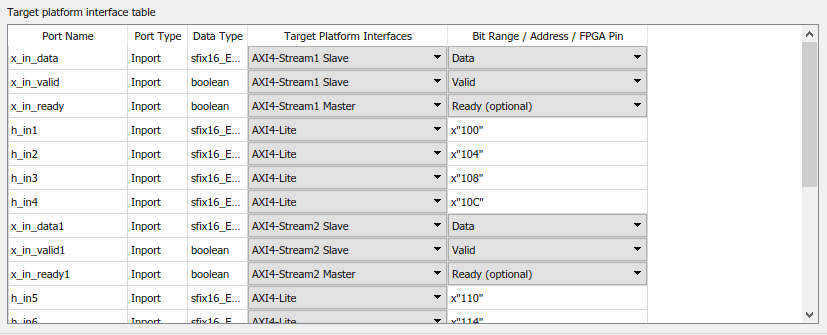

После применения настроек созданные интерфейсы отображаются в таблице Интерфейс целевой платформы (Target platform interface). После выполнения этой задачи указанные дополнительные интерфейсы сохраняются в подсистеме DUT в качестве свойства блока HDL AdditityTargetInterfaces.

При изменении дополнительных интерфейсов, уже сопоставленных портам DUT, например, при удалении или переименовании уже сопоставленного интерфейса, может быть потеряна информация о предыдущем сопоставлении интерфейсов. Затем порты отсоединяются от интерфейсов, и отображается раздел «Интерфейсы целевой платформы». No interface specified. Поэтому при внесении изменений в дополнительные целевые интерфейсы убедитесь, что порты DUT сопоставлены с соответствующими целевыми интерфейсами.

При создании собственного пользовательского ссылочного проекта можно добавить несколько интерфейсов AXI4-Stream, AXI4-Stream Video и AXI4 Master. В зависимости от типа добавляемого интерфейса укажите дополнительные интерфейсы с помощью addAXI4StreamInterface, addAXI4StreamVideoInterface, или addAXI4MasterInterface методы hdlcoder.ReferenceDesign класс.

Чтобы добавить дополнительные интерфейсы, в plugin_rd каждый раз, когда требуется добавить дополнительные интерфейсы, вызывайте метод интерфейса. В этом примере показано, как добавить два AXI4-Stream интерфейса.

function hRD = plugin_rd() % Reference design definition % Copyright 2017-2019 The MathWorks, Inc. % Construct reference design object hRD = hdlcoder.ReferenceDesign('SynthesisTool', 'Xilinx Vivado'); hRD.ReferenceDesignName = 'Multiple Interface Reference Design'; hRD.BoardName = 'ZedBoard'; % Tool information hRD.SupportedToolVersion = {'2019.1'}; % ... % ... % Add AXI4-Stream interface 1 hRD.addAXI4StreamInterface (... 'MasterChannelEnable', true, ... 'SlaveChannelEnable', true, ... 'MasterChannelConnection', 'axi_dma_s2mm/S_AXIS_S2MM', ... 'SlaveChannelConnection', 'axi_dma_mm2s/M_AXIS_MM2S', ... 'MasterChannelDataWidth', 32, ... 'SlaveChannelDataWidth', 32, ... 'InterfaceID', 'AXI4-Stream1'); % Add AXI4-Stream interface 2 hRD.addAXI4StreamInterface (... 'MasterChannelEnable', true, ... 'SlaveChannelEnable', true, ... 'MasterChannelConnection', 'ADC/S_AXIS_S2MM', ... 'SlaveChannelConnection', 'DAC/M_AXIS_MM2S', ... 'MasterChannelDataWidth', 32, ... 'SlaveChannelDataWidth', 32, ... 'InterfaceID', 'AXI4-Stream2'); % ... % ...

При запуске IP Core Generation workflow-процесс и целевой проект пользовательской ссылки Multiple Interface Reference Design, в Цели Набора Интерфейсная задача Вы можете нанести на карту порты DUT к каналам Владельца и Раба AXI4-Stream1 и каналам Владельца и Раба AXI4-Stream2.

Примечание

При назначении собственной пользовательской конструкции ссылки и сопоставлении дополнительных интерфейсов портам DUT в задаче Задать целевые интерфейсы (Set Target Interfaces) дополнительные интерфейсы не сохраняются в модели в качестве свойства блока HDL AdditiveTargetInterfaces. Вместо этого дополнительные интерфейсы сохраняются в пользовательской ссылочной конструкции в plugin_rd.m файл.

Можно также динамически настраивать ссылочную конструкцию для указания количества добавляемых интерфейсов и свойств интерфейса.

В plugin_rd создайте ссылочный параметр конструкции для количества дополнительных интерфейсов, которые требуется добавить.

Создайте функцию обратного вызова, которая имеет различные варианты для количества интерфейсов, которые вы хотите добавить, а затем ссылайтесь на функцию в plugin_rd с помощью CustomizeReferenceDesignFcn способ hdlcoder.ReferenceDesign класс.

Дополнительные сведения см. в разделе Настройка конструкции привязок динамически на основе параметров конструкции привязок.

При использовании одного потокового канала HDL Coder™ автоматически генерирует сигнал Ready и соответствующую логику обратного давления.

При использовании нескольких каналов потоковой передачи кодер HDL не создает автоматически логику обратного давления. В этом случае генерируется сигнал готовности, но главный сигнал готовности на входе игнорируется, а ведомый сигнал готовности на выходе привязывается к высокому значению. Отсутствие логики обратного давления может привести к падению образцов. Если требуется применить противодавление к ведомому интерфейсу или ответить на противодавление от главного интерфейса, необходимо смоделировать сигнал Ready для каждого дополнительного интерфейса, а затем сопоставить порт с сигналом Ready для этого интерфейса. Если модель не выполняется, задача Задать целевой интерфейс (Set Target Interface) отображает предупреждение, содержащее имена интерфейсов, которым требуется порт Ready. Если вам не нужно применять противодавление или реагировать на него, вы можете проигнорировать это предупреждение, и вам не придется моделировать сигнал Ready.

При использовании нескольких интерфейсов AXI4-Stream, если требуется применить противодавление к подчиненному интерфейсу или ответить на противодавление от главного интерфейса, необходимо смоделировать сигнал Ready для каждого дополнительного интерфейса, а затем сопоставить порт с сигналом Ready для этого интерфейса. Сведения о том, как формируется логика противодавления для одного канала потоковой передачи и как моделировать сигнал готовности, см. в разделе Сигнал готовности (необязательно).

При запуске общего рабочего процесса генерации IP Core можно указать тип интерфейса и пользовательский идентификатор интерфейса для каждого дополнительного интерфейса. Другие свойства интерфейса, такие как ширина данных, не могут быть настроены и использовать значения по умолчанию. При создании собственной пользовательской ссылочной конструкции можно настроить имя интерфейса и свойства интерфейса.

При сопоставлении портов DUT с несколькими каналами интерфейса AXI4-Stream можно использовать только скалярные порты. В векторных портах могут быть самое большее один канал Владельца AXI4-потока и один Рабский канал AXI4-потока.

Xilinx ® Zynq ® -7000 или Intel ® Quartus ® Prime должны быть целевой платформой.

Синхронизация процессора/FPGA должна быть Free running.

Xilinx Vivado ® или Intel Quartus Prime должны быть вашим инструментом синтеза.