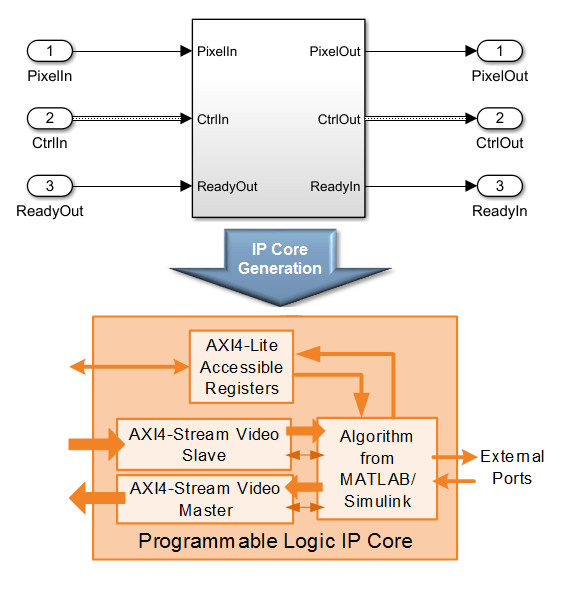

Программное обеспечение HDL Coder™ позволяет реализовать в модели упрощенный потоковый пиксельный протокол. Программное обеспечение генерирует IP-ядро HDL с AXI4-Stream видеоинтерфейсами.

Вы можете использовать текущий пиксельный протокол для отображения интерфейса AXI4-Stream Video. Алгоритмы видео обрабатывают данные последовательно и генерируют видеоданные как последовательный поток пиксельных данных и управляющих сигналов. Сведения о потоковом пиксельном протоколе см. в разделе Потоковый пиксельный интерфейс (панель инструментов Vision HDL).

Чтобы создать ядро IP с интерфейсами AXI4-Stream Video, в интерфейсе DUT реализуйте следующие сигналы:

Пиксельные данные

Шина управления пикселами

Шина пиксельного управления - это шина, которая имеет следующие сигналы:

hStart

hEnd

vStart

vEnd

valid

Сигналы hStart и hEnd представляют начало активной линии и конец активной линии соответственно. Сигналы vStart и vEnd представляют начало и конец кадра.

При необходимости можно смоделировать сигнал противодавления (Ready) и сопоставить его с интерфейсом AXI4-Stream Video.

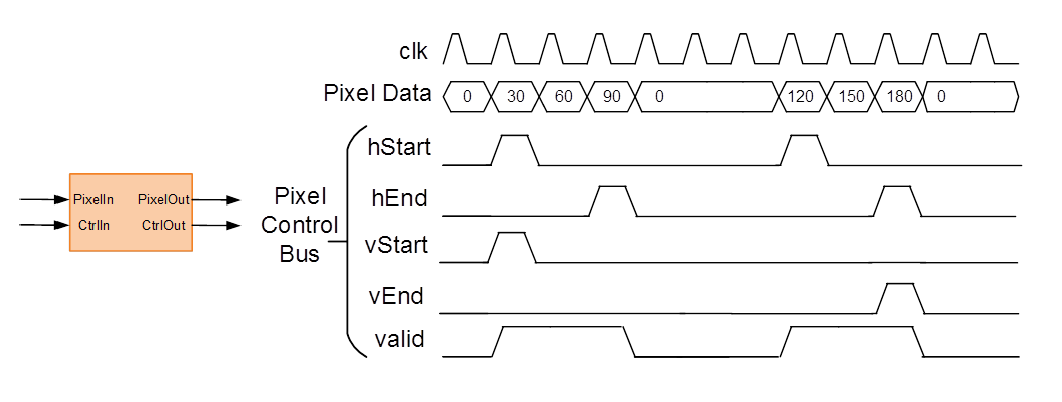

Этот рисунок представляет собой изображение размером 2 на 3 пиксела. Активной областью изображения является прямоугольник с пунктирной линией вокруг него и неактивные пикселы, которые его окружают. Пикселы помечаются значениями в градациях серого.

![]()

На этом рисунке показана временная диаграмма для сигналов Pixel Data и Pixel Control Bus, моделируемых в интерфейсе DUT.

Сигнал пиксельных данных является первичным видеосигналом, который передается через интерфейс AXI4-Stream Video. Когда сигнал Pixel Data является действительным, утверждается действительный сигнал.

Сигнал hStart становится высоким в начале активных линий. Сигнал hEnd становится высоким в конце активных линий.

Сигнал vStart становится высоким в начале активного кадра во второй строке. Сигнал vEnd становится высоким в конце активного кадра в третьей строке.

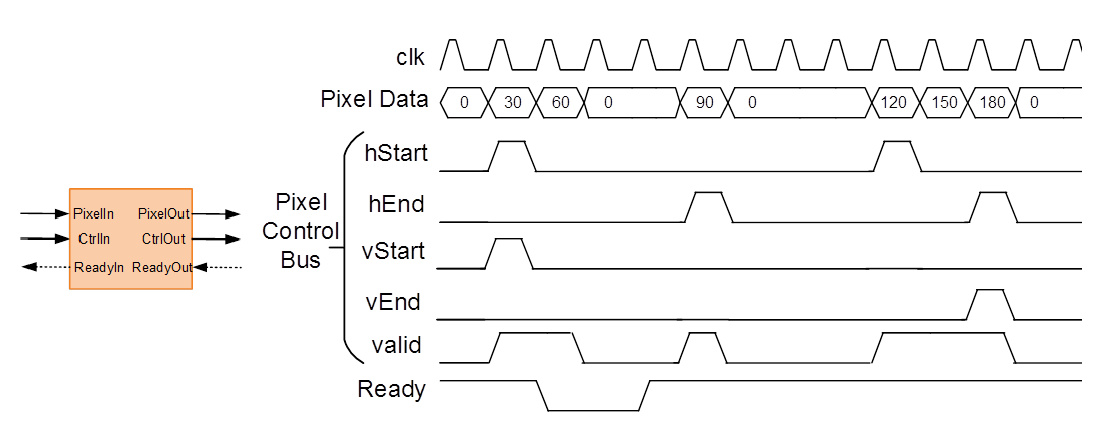

На этом рисунке показана временная диаграмма для пиксельных данных, шины управления пикселями и сигнала готовности, моделируемого в интерфейсе DUT.

При сопоставлении портов DUT с интерфейсом AXI4-Stream Video можно дополнительно смоделировать сигнал противодавления Ready и сопоставить его с интерфейсом AXI4-Stream Video.

В подчиненном интерфейсе с сигналом Ready можно применить противодавление. В главном интерфейсе с сигналом Ready можно реагировать на обратное давление.

При моделировании сигнала Ready в AXI4-Stream видеоинтерфейсах главный интерфейс должен сбросить свой действительный сигнал через один цикл после того, как сигнал Ready будет сброшен.

Если не моделировать сигнал готовности, кодер HDL генерирует соответствующую логику противодавления.

Можно смоделировать алгоритм видео с помощью сигналов Pixel Data и Pixel Control Bus на портах DUT и сопоставить сигналы с интерфейсами AXI4-Stream Video. При необходимости можно смоделировать сигнал противодавления (Ready) и сопоставить его с интерфейсом AXI4-Stream Video.

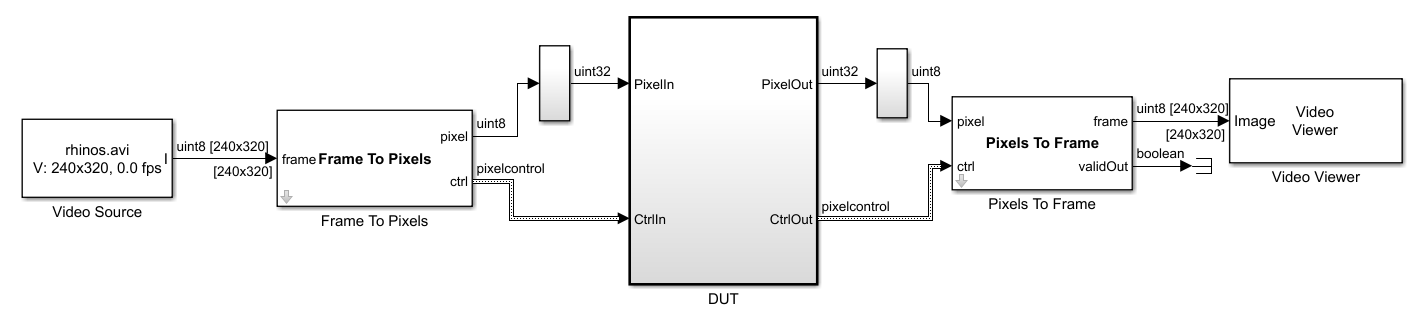

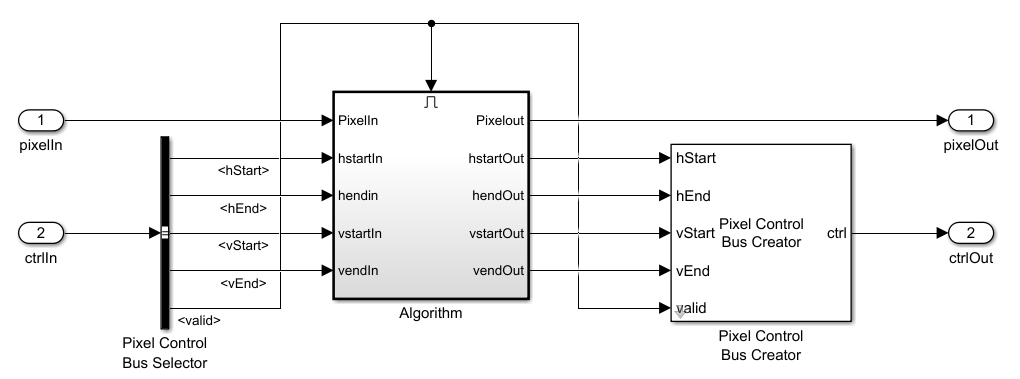

На этом рисунке показан пример модели Simulink ® верхнего уровня с вводом источника видео.

Блоки «от кадра до пикселей» и «от пикселей до кадра» выполняют преобразование между видеокадрами и шиной управления пикселями и данными пикселей в интерфейсе DUT. Для использования этих блоков необходимо установить Toolbox™ Vision HDL.

См. также «От кадра до пикселей» (панель инструментов Vision HDL) и «От пикселей до кадра» (панель инструментов Vision HDL).

На этом рисунке показано, как моделировать сигналы Pixel Data и Pixel Control Bus в подсистеме DUT.

Можно непосредственно подключить действительный сигнал от шины управления пикселями к порту Enable. Если у вас нет программного обеспечения Vision HDL Toolbox, замените блоки Pixel Control Bus Selector и Pixel Control Bus Creator блоками Bus Selector и Bus Creator соответственно.

Интерфейсы AXI4-Stream Video в DUT могут дополнительно включать сигнал Ready.

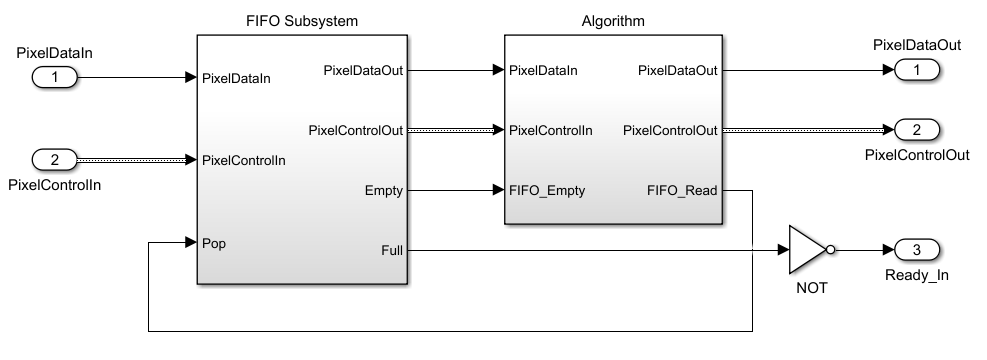

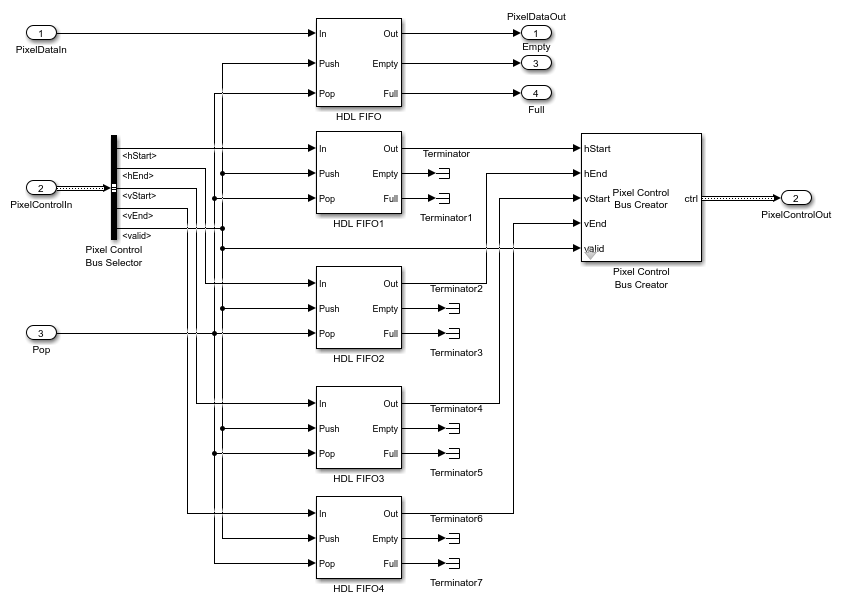

Например, в DUT можно установить FIFO для хранения некоторых видеоданных перед обработкой сигналов. Используйте подсистему FIFO, которая содержит блоки HDL FIFO, для хранения сигналов Pixel Data и Pixel Control Bus. Чтобы применить противодавление к предшествующему компоненту, смоделируйте сигнал Ready на основе сигнала FIFO Full.

На этом рисунке показано, как моделировать сигнал Ready в подсистеме DUT.

Блок подсистемы FIFO использует блоки HDL FIFO для данных пикселей и для сигналов шины управления пикселями.

Отключить балансировку задержки для тракта сигнала Ready. Если включить балансировку задержки, кодер может вставить одну или несколько задержек в сигнал Ready.

При запуске IP Core Generation можно сопоставить несколько портов DUT с каналами AXI4-Stream Video Master и AXI4-Stream Video Slave. Порты DUT, сопоставленные с несколькими интерфейсными каналами, должны использовать скалярный тип данных. При использовании векторных портов эти порты можно сопоставить не более чем с одним каналом AXI4-Stream Video Master и одним каналом AXI4-Stream Video Slave.

Дополнительные сведения см. в разделе Создание IP-ядра HDL с несколькими AXI4-Stream и основными интерфейсами AXI4.

Программное обеспечение HDL Coder поддерживает проекты с несколькими частотами выборки при запуске рабочего процесса генерации IP Core. При сопоставлении портов интерфейса с интерфейсами AXI4-Stream Video Master или AXI4-Stream Video Slave для использования нескольких скоростей дискретизации убедитесь, что порты DUT, которые сопоставляются с этими интерфейсами AXI4, работают с самой высокой скоростью проектирования после генерации кода HDL.

Дополнительные сведения см. в разделе Создание многоскоростного ядра IP.

Системы видеосъемки сканируют видеосигналы слева направо и сверху вниз. По мере сканирования эти системы генерируют неактивные интервалы между строками и кадрами активного видео. Этот неактивный интервал называется верандой видео. Горизонтальное крыльцо состоит из неактивных циклов между концом одной строки и началом следующей строки. Вертикальное крыльцо состоит из неактивных циклов между конечной активной линией одной рамы и начальной активной линией следующей рамы.

На этом рисунке показан видеокадр с горизонтальным крыльцом, разделенным на передний и задний крыльцо.

![]()

Для интерфейса AXI4-Stream Video не требуется видеопорша, но алгоритмы Vision HDL Toolbox требуют веранды для обработки видеопотоков. Если входящий поток пикселей не имеет достаточной части, кодер HDL вставляет требуемую часть в поток пикселей. Используя регистры AXI4-Lite в сгенерированном ядре IP, можно настроить следующие параметры веранды для каждого видеокадра:

Активные пикселы на строку (по умолчанию: 1920)

Активные видеолинии: (По умолчанию: 1080)

Длина горизонтального крыльца (по умолчанию: 280)

Вертикальная длина крыльца (по умолчанию: 45)

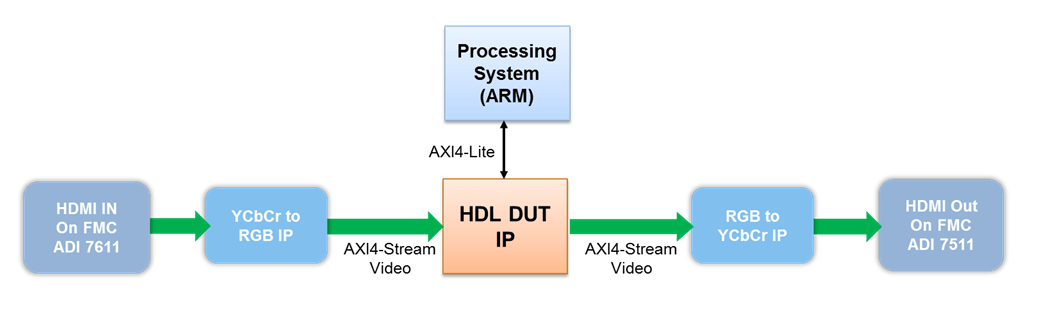

Сгенерированное IP-ядро HDL можно интегрировать с AXI4-Stream видеоинтерфейсами в Default video system эталонный проект.

Этот рисунок представляет собой блок-схему Default video system эталонная архитектура конструкции.

Вы можете использовать это Default video system эталонная архитектура проектирования с этими целевыми платформами:

Xilinx Zynq ZC702 evaluation kit

Xilinx Zynq ZC706 evaluation kit

ZedBoard

Для использования Default video system необходимо установить пакет поддержки Computer Vision Toolbox™ для аппаратных средств на базе Xilinx ® Zynq ®.

При сопоставлении портов DUT с AXI4-Stream видеоинтерфейсами:

Порт DUT, сопоставленный сигналу Pixel Data, должен использовать скалярный тип данных.

Zynq-7000 Xilinx должна быть целевой платформой.

В качестве средства синтеза необходимо использовать Xilinx Vivado ®.

Синхронизация процессора/FPGA должна быть Free running.