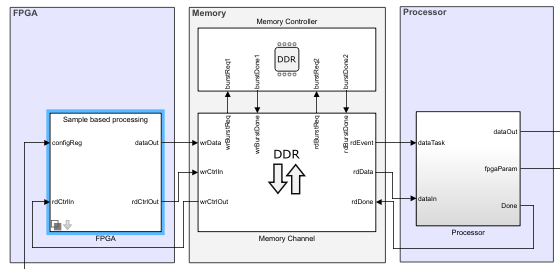

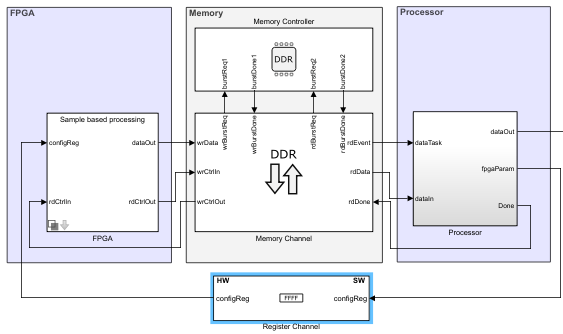

Канал памяти моделирует передачу данных от FPGA к процессору с использованием совместно используемой внешней памяти. Канал регистра моделирует управление логикой FPGA от процессора. Можно настроить логику FPGA и считывать состояние логики FPGA с процессора. В следующих разделах показано, как создавать эти канальные соединения.

Откройте окно soc_hwsw_top.slx модель.

Добавление блока канала памяти и блока контроллера памяти в Memory область. Вместе эти блоки моделируют соединение памяти через DDR между процессорами и FPGA вашего приложения.

Откройте маску диалогового окна блока контроллера памяти. Задать для параметра «Количество основных объектов» значение 2. На вкладке Дополнительно (Advanced) контроллер памяти автоматически наследует параметры от платы аппаратного обеспечения, указанной в конфигурациях модели.

Подключите пару пакетных портов контроллера памяти, burstReq и burstDone, к портам запроса пакета чтения и записи блока канала памяти.

В модели откройте маску диалогового окна «Канал памяти». Задайте для типа канала значение AXI4-Stream to Software via DMA. Установить размер буфера (байт) в FrameSize*4 и количество буферов для 6. Нажмите кнопку ОК.

Добавление блока канала регистрации в модель и подключение блока к Processor и FPGA подсистем, как показано на следующем рисунке.

Откройте маску диалогового окна «Регистрация блока канала». Добавьте новый регистр с этими свойствами.

| Зарегистрироваться | Направление | Тип данных | Измерение |

|---|---|---|---|

| configReg | Написать | uint8 | 1 |

Установить время выборки записи регистра в FPGASSTime. Нажмите кнопку «» ОК «». Этот пример времени задан в файле soc_hwsw_init.m.

Канал памяти | Контроллер памяти | Зарегистрировать канал