Помощник по рабочим процессам HDL предлагает рабочий процесс для проверки алгоритма совместимости HDL, создания кода HDL, проверки кода и последующего развертывания кода на целевой платформе.

Можно запустить помощник по рабочим процессам для алгоритма MATLAB ® или модели Simulink ®. Перед развертыванием кода на целевой аппаратной платформе установите средство синтеза и укажите путь к этому средству синтеза с помощью hdlsetuptoolpath функция. См. раздел Настройка инструмента.

Перед заданием целевого рабочего процесса при запуске помощника по рабочим процессам из MATLAB укажите файлы проекта и тестового стенда, определите типы ввода и выполните преобразование с фиксированной точкой.

Чтобы указать целевой рабочий процесс, выполните следующие действия.

На панели инструментов MATLAB на вкладке Приложения выберите приложение Кодер HDL.

Выберите файлы проектирования и тестирования MATLAB и нажмите кнопку «Помощник по рабочим процессам».

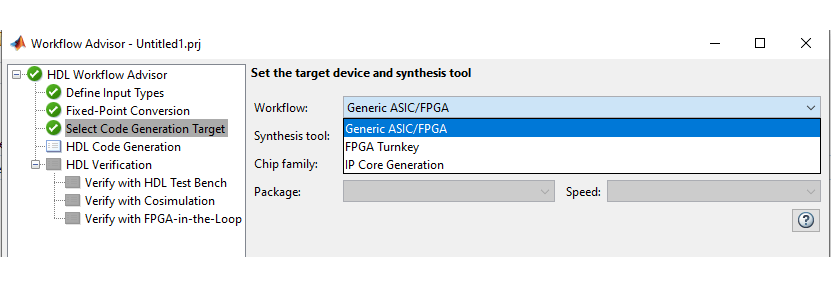

В помощнике по рабочим процессам на задании «Выбор цели создания кода» выберите рабочий процесс.

Шаги после выбора цели создания кода изменяются в зависимости от целевого рабочего процесса.

При запуске помощника по рабочим процессам из модели Simulink независимо от целевого рабочего процесса выполняются шаги по подготовке модели к созданию кода HDL, а затем создается код.

Откройте модель Simulink, для которой необходимо запустить рабочий процесс.

На панели инструментов Simulink на вкладке Apps выберите приложение HDL Coder.

На вкладке Код HDL (HDL Code) нажмите кнопку Помощник по рабочим процессам (Workflow Advisor).

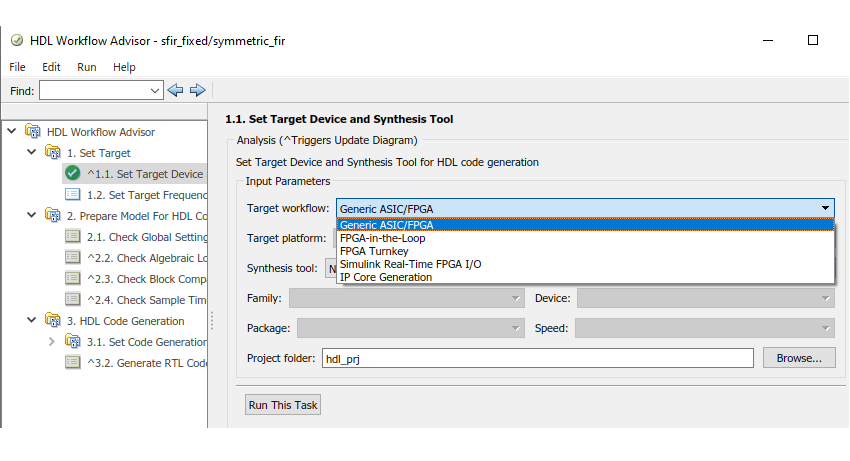

В помощнике по рабочим процессам HDL в задаче Задать целевое устройство и средство синтеза выберите целевой рабочий процесс.

Шаги помощника по рабочим процессам изменяются в зависимости от целевого рабочего процесса, целевой платформы и средства синтеза. В следующих разделах описаны дополнительные сведения о каждом из этих рабочих процессов.

Создайте код HDL из модели Simulink или алгоритма MATLAB, проверьте код HDL и разверните его на универсальном ASIC или FPGA-устройстве. Можно выбрать из семейства устройств, относящихся к этим инструментам синтеза, как указано в разделе Общее оборудование ASIC/FPGA.

Используя этот рабочий процесс, можно:

Создайте код HDL для алгоритма MATLAB с фиксированной точкой или модели Simulink, совместимой с HDL.

Создайте тестовый стенд HDL и стенд косимуляции (требуется Verifier™ HDL), а также скрипты для создания и запуска кода и тестового стенда. При запуске Simulink HDL Workflow Advisor можно также создать тестовый стенд SystemVerilog DPI и покрытие кода (требуется проверка HDL).

Выполняйте синтез FPGA и анализ синхронизации, а также быстро создавайте прототипы на универсальных платформах FPGA за счет интеграции со средствами синтеза сторонних производителей.

Обратная аннотация модели с информацией о критическом пути и другой информацией, полученной в процессе синтеза, и оптимизация конструкции по площади и скорости.

Примечание

При выборе Intel Quartus Pro или Microsemi Libero SoC как инструмент синтеза, задача Аннотировать модель с результатом синтеза (Annotate Model with Synthesis Result) недоступна. Чтобы просмотреть критический путь, запустите workflow-процесс для синтеза, а затем откройте отчеты о времени.

Дополнительные сведения см. в следующих разделах:

Развертывание модели Simulink или алгоритма MATLAB на автономных платах FPGA и платформах SoC. Чтобы использовать этот рабочий процесс, необходимо выбрать VHDL как Язык. Можно выбрать один из этих инструментов синтеза, как указано в документе Оборудование FPGA под ключ.

Используйте этот рабочий процесс для:

Выберите из диспетчера плат FPGA платы, которые включены под ключ, или создайте собственные настраиваемые платы для развертывания.

Создание кода HDL для всей конструкции FPGA, алгоритма DUT и кода HDL верхнего уровня оболочки FPGA. Можно также задать ограничения сопоставления контактов.

Выполняйте синтез FPGA и анализ синхронизации, а также быстро создавайте прототипы на платформах FPGA и SoC за счет интеграции со сторонними средствами синтеза.

Пример см. в разделе Начало работы с потоком операций FPGA под ключ.

Создайте код RTL и пользовательское IP-ядро HDL из модели Simulink или алгоритма MATLAB. Перед запуском рабочего процесса разбейте проект на компоненты, работающие на программном обеспечении, и компоненты, работающие на оборудовании. См. раздел Рабочий процесс совместного проектирования аппаратного и программного обеспечения для платформ SoC.

Ядро IP - это совместно используемый и многократно используемый компонент HDL, который состоит из файлов определения ядра IP, кода HDL, созданного для вашего алгоритма, файла заголовка C с картой адресов регистров и отчета ядра IP. См.:

Вы можете выбрать один из этих инструментов синтеза, как указано в IP Core Generation Hardware.

Используйте этот рабочий процесс для:

Создайте общее независимое от платы ядро Xilinx ® или Intel ® HDL IP.

Интегрируйте ядро IP в эталонную конструкцию для целевых автономных плат FPGA или платформ SoC с помощью интегратора Xilinx Vivado ® IP или Intel Qsys.

Взаимодействие с сгенерированным IP-ядром HDL с помощью встроенного процессора ARM или от MATLAB с помощью средства проверки HDL MATLAB в качестве мастера AXI. См. раздел Настройка для MATLAB AXI Master (HDL Verifier).

Вы можете интегрировать IP-ядро ЛПВП в ЛПВП Coder™ предоставленные эталонные проекты, такие как default system reference design или в созданную ссылочную конструкцию. Дополнительные сведения см. в следующих разделах:

Создание кода HDL из модели Simulink и развертывание кода на модулях ввода-вывода Speedgoat FPGA. Этот рабочий процесс требует Xilinx Vivado и использует IP Core Generation инфраструктура потока операций, как упомянуто в Simulink Real-Time FPGA I/O: Speedgoat Target Hardware.

Для запуска Simulink Real-Time FPGA I/O установите библиотеку Speedgoat Library и пакеты интеграции кодеров HDL Speedgoat. После установки интеграционных пакетов можно выбрать целевую платформу, а затем запустить рабочий процесс для:

Создание многоразового и совместно используемого ядра IP.

Интеграция IP-ядра в эталонный проект Speedgoat.

Создайте битовый поток FPGA и загрузите его на целевое оборудование.

Создайте модель Simulink Real-Time™. Модель представляет собой модель интерфейсной подсистемы, которая содержит блоки для программирования FPGA и связи с платой во время выполнения в реальном времени.

Дополнительные сведения см. в разделе Рабочий процесс генерации IP Core для программируемых модулей ввода-вывода Speedgoat Simulink.

Протестируйте модель Simulink или алгоритм MATLAB на целевом FPGA. Этот рабочий процесс требует проверки HDL. Можно выбрать один из этих инструментов синтеза, перечисленных в FPGA-in-the-Loop Hardware.

Используйте этот рабочий процесс для:

Выберите в FPGA Board Manager платы с поддержкой FIL или создайте собственные пользовательские платы для проверки. См. раздел Настройка платы FPGA.

Создайте код HDL для алгоритма MATLAB с фиксированной точкой или модели Simulink, совместимой с HDL.

Выполните реализацию FPGA и подключитесь к целевой плате FPGA с помощью Ethernet, JTAG или PCI Express для моделирования FIL.

Дополнительные сведения см. в следующих разделах: