HDL Workflow Advisor предлагает рабочий процесс, чтобы можно было проверить алгоритм на совместимость с HDL, сгенерировать HDL-код, проверить код, а затем развернуть код на целевой платформе.

Можно запустить советник по рабочему процессу для MATLAB® алгоритм или Simulink® модель. Прежде чем развертывать код на целевой аппаратной платформе, установите инструмент синтеза и укажите путь к этому инструменту синтеза с помощью hdlsetuptoolpath функция. См. Setup инструмента»

Прежде чем вы задаете целевой рабочий процесс, при запуске Workflow Advisor из MATLAB задайте файлы проекта и испытательного стенда, задайте типы входа и запустите преобразование с фиксированной точкой.

Чтобы задать целевой рабочий процесс:

На панели инструментов MATLAB на вкладке Apps выберите приложение HDL Coder.

Выберите проект MATLAB и испытательного стенда файлы и нажмите кнопку Workflow Advisor.

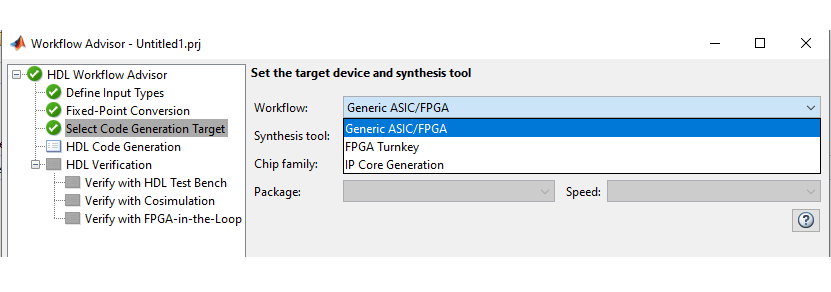

В Workflow Advisor, на Select Code Generation Target задаче, выберите Workflow.

Шаги после целевого выбора генерации кода изменяются в зависимости от вашего целевого рабочего процесса.

Когда вы запускаете Workflow Advisor из модели Simulink, независимо от целевого рабочего процесса, вы запускаете шаги, чтобы подготовить модель к генерации HDL-кода, а затем генерируете код.

Откройте модель Simulink, для которой вы хотите запустить рабочий процесс.

На панели инструментов Simulink на вкладке Apps выберите приложение HDL Coder.

На вкладке HDL Code нажмите кнопку Workflow Advisor.

В HDL Workflow Advisor, на Set Target Device and Synthesis Tool задаче, выберите Target workflow.

Шаги в Workflow Advisor изменяются в зависимости от Target workflow, Target platform и Synthesis tool. В следующих разделах приведены дополнительные сведения о каждом из этих рабочих процессов.

Сгенерируйте HDL-код из вашей модели Simulink или алгоритма MATLAB, проверьте HDL-код и разверните код на типовом устройстве ASIC или FPGA. Можно выбрать из семейства устройств, которые относятся к этим инструментам синтеза, как указано в Generic ASIC/FPGA Hardware.

При помощи этого рабочего процесса можно:

Сгенерируйте HDL-код для алгоритма MATLAB с фиксированной точкой или для HDL-совместимой модели Simulink.

Сгенерируйте HDL- испытательного стенда и испытательного стенда косимуляции (требует HDL- Verifier™), а также скрипты для создания и запуска кода и испытательного стенда. Можно также сгенерировать испытательные стенды SystemVerilog DPI и покрытие кода при запуске Simulink HDL Workflow Advisor (требует HDL Verifier).

Выполните синтез и анализ времени FPGA и быстро прототипируйте свой проект на типовых платформах FPGA путем интегрирования с инструментами синтеза сторонних производителей.

Обратная аннотация модели с помощью информации о критическом пути и другой информации, полученной во время синтеза, и оптимизация вашего проекта для площади и скорости.

Примечание

Если вы выбираете Intel Quartus Pro или Microsemi Libero SoC как Synthesis tool, Annotate Model with Synthesis Result задача недоступна. Чтобы увидеть критический путь, запустите рабочий процесс для синтеза, а затем откройте отчеты о синхронизации.

Для получения дополнительной информации см.:

Разверните свою модель Simulink или алгоритм MATLAB на автономных платах FPGA и однокристальных платформах. Чтобы использовать этот рабочий процесс, необходимо выбрать VHDL как Language. Можно выбрать один из этих инструментов синтеза, как указано в FPGA Turnkey Hardware.

Используйте этот рабочий процесс для:

Выберите платы из диспетчера плат FPGA, которые будут Turnkey Enabled, или создайте свои собственные пользовательские платы для развертывания.

Сгенерируйте HDL-код для всего проекта FPGA, алгоритма DUT и HDL-кода верхнего уровня обертки FPGA. Можно также задать ограничения отображения контактов.

Выполните синтез и анализ времени FPGA и быстро прототипируйте свой проект на платформах FPGA и SoC путем интегрирования с инструментами синтеза сторонних производителей.

Для получения примера смотрите Рабочий процесс «Начало работы с FPGA под ключ».

Сгенерируйте код RTL и пользовательское IP-ядро HDL из вашей модели Simulink или алгоритма MATLAB. Прежде чем запускать рабочий процесс, разделите проект на компоненты, которые запускаются на программном обеспечении и компонентах, которые запускаются на оборудовании. Смотрите рабочий процесс «Совместное проектирование аппаратного и программного обеспечения» для однокристальных платформ.

IP-ядро является совместно используемым и переиспользуемым HDL компонентом, который состоит из файлов определения ядра IP, HDL-кода, сгенерированного для вашего алгоритма, заголовочного файла C с адресной картой регистра и отчета ядра IP. См.:

Вы можете выбрать один из этих инструментов синтеза, как указано в IP Core Generation Hardware.

Используйте этот рабочий процесс для:

Сгенерируйте независимую от типовой платы Xilinx® или Intel® IP-ядро HDL.

Интеграция IP-ядра в исходный проект для использования автономных плат FPGA или однокристальных платформ с Xilinx Vivado® IP-интегратор или Intel Qsys.

Общайтесь с сгенерированным IP-ядром HDL с помощью встроенного процессора ARM или из MATLAB с помощью HDL Verifier MATLAB в качестве AXI Master. См. раздел Настройка для MATLAB AXI Master (HDL Verifier).

Можно интегрировать ядро IP HDL в HDL- Coder™, такие как default system reference design или в исходный проект, которую вы создали. Для получения дополнительной информации см.:

Сгенерируйте HDL-код из вашей модели Simulink и разверните код на модулях ввода-вывода Speedgoat FPGA. Этот рабочий процесс требует Xilinx Vivado и использует IP Core Generation инфраструктура рабочего процесса, как упомянуто в Simulink Real-Time FPGA I/O: Speedgoat Target Hardware.

Чтобы запустить Simulink Real-Time FPGA I/O рабочий процесс, установите библиотеку Speedgoat и пакеты HDL Coder Интегрирования Speedgoat. После установки пакетов интегрирования можно выбрать Target platform, а затем запустить рабочий процесс в:

Сгенерируйте переиспользуемое и совместно используемое IP-ядро.

Интеграция ядра IP с исходным проектом Speedgoat.

Сгенерируйте битовый поток FPGA и загрузите битовый поток на целевой компьютер.

Сгенерируйте модель Simulink Real-Time™. Модель является моделью интерфейсной подсистемы, которая содержит блоки для программирования FPGA и связи с платой во время выполнения в реальном времени.

Для получения дополнительной информации смотрите рабочий процесс генерации IP-ядра для программируемых модулей ввода-вывода Speedgoat Simulink.

Протестируйте свою модель Simulink или алгоритм MATLAB на целевом FPGA. Для этого рабочего процесса требуется HDL Verifier. Можно выбрать один из этих инструментов синтеза, как указано в Цикл Hardware.

Используйте этот рабочий процесс для:

Выберите платы из FPGA Board Manager, которые FIL Enabled, или создайте свои собственные пользовательские платы для верификации. См. раздел Индивидуальную настройку платы FPGA.

Сгенерируйте HDL-код для алгоритма MATLAB с фиксированной точкой или для HDL-совместимой модели Simulink.

Выполните реализацию FPGA и подключите к целевой плате FPGA с помощью Ethernet, JTAG или PCI Express для симуляции FIL.

Для получения дополнительной информации см.:

FIL- Симуляции с HDL Workflow Advisor для Simulink (HDL Verifier)

Симуляция FIL с помощью HDL Workflow Advisor для MATLAB (HDL Verifier)