Рабочие процессы генерации компонентов SystemVerilog DPI и универсальной методологии верификации (UVM) испытательного стенда генерации позволяют вам повторно использовать Simulink® модели верификации в получившемся SystemVerilog. Блоки верификации модели Simulink, такие как Assertion (Simulink) или Check Dynamic Lower Bound (Simulink), и вызовы verify (Simulink Test) операторы создают проверки ошибок и функциональные точки покрытия в сгенерированном SystemVerilog.

Когда assertion или verify Simulink сбой вызова, он генерирует ошибку SystemVerilog по умолчанию. Когда любой из них успешен, он генерирует точку покрытия SystemVerilog, которая регистрирует результат PASS. Утверждения и verify Поведение оператора можно настроить с помощью аргументов командной строки SystemVerilog и блока HDL Verifier Assertion. Для получения дополнительной информации о индивидуальной настройке см. раздел Настройка Assertion.

В Simulink создайте модель для тестируемого устройства (DUT), а затем создайте испытательный стенд для модели. Можно использовать комбинацию блоков утверждения из библиотеки Simulink/Model Verification и блоков, которые содержат verify операторы из библиотеки Simulink Test, такие как:

A verify Оператор (Simulink Test)

Блок из библиотеки Верификации модели (Simulink)

Блок HDL Verifier™ Assertion

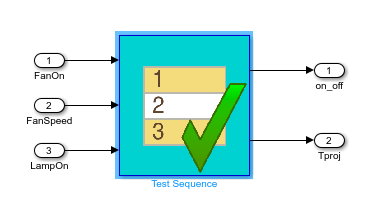

В вашей тестовой модели включите verify оператор путем добавления одного или нескольких из следующих блоков:

Test Assessment (Simulink Test)

Test Sequence (Simulink Test)

Chart (Stateflow)

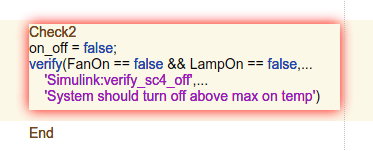

Чтобы создать и изменить шаги тестирования, используйте Редактор тестовых последовательностей (Simulink Test). В тестовой последовательности используйте verify операторы для оценки симуляции, как описано в Test Sequence and Assessment Syntax (Simulink Test).

The verify оператор и блок Test Sequence представляют временную проверку в Simulink. Когда вы генерируете компонент DPI SystemVerilog, временная логика находится в сгенерированном коде C. Оболочка SystemVerilog содержит немедленное подтверждение, которое запускается при нарушении условия проверки.

Можно также включить эти блоки утверждений из библиотеки Simulink/Model Verification (Simulink).

Assertion (Simulink)

Check Dynamic Gap (Simulink)

Check Dynamic Range (Simulink)

Check Static Gap (Simulink)

Check Static Range (Simulink)

Check Dynamic Lower Bound (Simulink)

Check Dynamic Upper Bound (Simulink)

Check Input Resolution (Simulink)

Check Static Lower Bound (Simulink)

Check Static Upper Bound (Simulink)

Check Discrete Gradient (Simulink)

В сложение можно включить блок HDL Verifier Assertion для создания настраиваемых утверждений. Пример, в котором используется блок HDL Verifier Assertion, см. в разделе «Генерация собственных утверждений SystemVerilog из Simulink».

В SystemVerilog каждая модель верификации блока и verify оператор сопоставлен с утверждением и точкой покрытия. Можно настроить цели покрытия, отфильтровать определенные утверждения и просмотреть подробную информацию для каждого из операторов проверки.

Можно использовать несколько verify операторы и блоки утверждений в вашей модели.

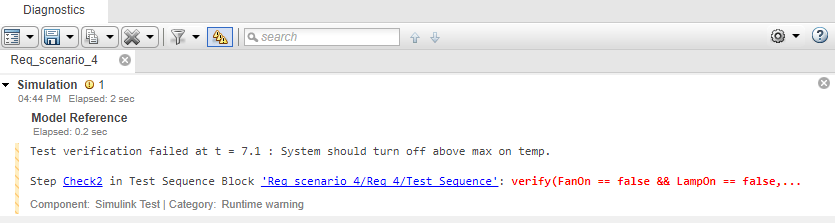

При симуляции вашего проекта в Simulink, симуляция предупреждает, задано ли verify ошибка оценки.

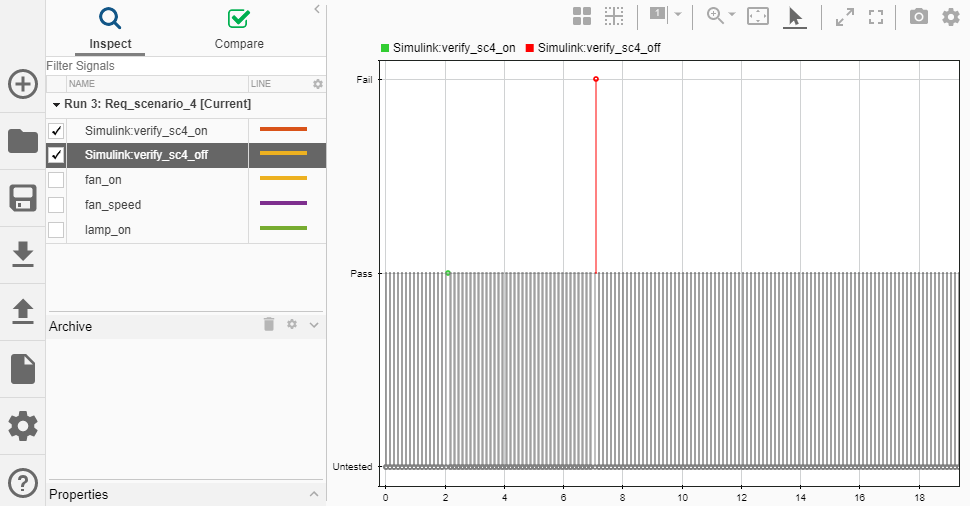

Можно просматривать и просматривать результаты симуляции при помощи Simulation Data Inspector (Simulink). Откройте Simulation Data Inspector, введя этот код в MATLAB® командная строка.

Simulink.sdi.view

Чтобы просмотреть сигналы во времени, выберите их в левой панели Simulation Data Inspector.

Непосредственную настройку SystemVerilog можно настроить двумя способами:

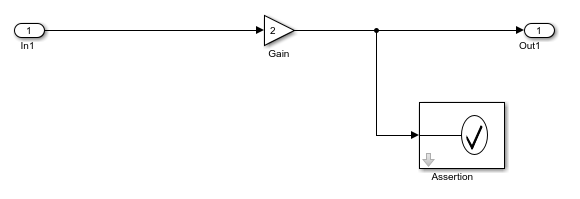

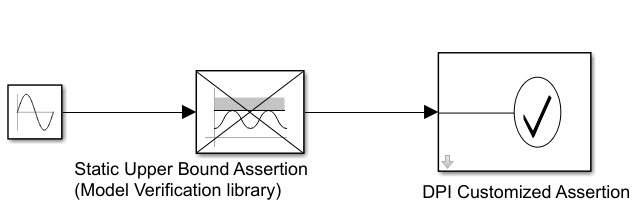

Включите HDL Verifier Assertion блок и настройте сгенерированное значение SystemVerilog немедленно. Вы можете задать пользовательское сообщение, когда сбой утверждения и можете выбрать между предупреждением, ошибкой или пользовательской командой, когда сбой утверждения. Пример, в котором используется блок HDL Verifier Assertion, см. в разделе «Генерация собственных утверждений SystemVerilog из Simulink». Результат аналогичен этому рисунку.

Чтобы настроить проверку типа «assertion» из библиотеки Верификации модели, соедините выход блоков с настраиваемым блоком Assertion HDL Verifier путем выполнения следующих шагов.

Добавьте блок из библиотеки Simulink/Model Verification к своей модели.

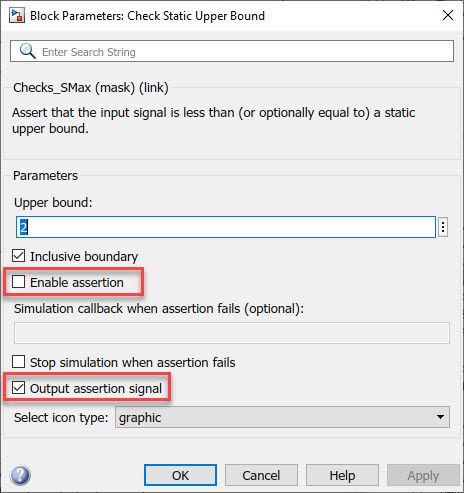

Откройте маску блока, а затем установите эти параметры (как показано на этом рисунке):

Очистите параметр Enable assertion, чтобы предотвратить избыточные выходы значения.

Выберите параметр Output assertion signal, чтобы создать логический выходной сигнал, который захватывает значения.

Добавьте блок Assertion из библиотеки HDL Verifier / For Use with DPI-C SystemVerilog и соедините выходной сигнал блока Model Verification с входным портом блока Assertion.

Настройте блок Assertion путем следования шагам в примере рабочего процесса «Генерация утверждений».

Результат аналогичен этому рисунку.

В диалоговом окне Параметры конфигурации выберите Code Generation в левой панели. В разделе Target Selection установите System Target File равным systemverilog_dpi_grt.tlc или к systemverilog_dpi_ert.tlc при использовании Embedded Coder®.

Выберите SystemVerilog DPI на левой панели. В разделе SystemVerilog Ports установите тип данных и настройки соединения. Нажмите OK.

Примечание

Чтобы сгенерировать компонент UVM или DPI, блок assertion или test должен находиться внутри подсистемы Simulink.

В Simulink щелкните правой кнопкой мыши блок подсистемы, который содержит тестовую последовательность, и выберите C/C++ Code > Build This Subsystem. Нажмите Build в открывшемся диалоговом окне.

Также можно использовать командную строку MATLAB для генерации компонента DPI. Используйте slbuild (Simulink) функция для создания системы. Например, чтобы создать подсистему с именем «My_verify_tst,», введите этот код в командной строке MATLAB.

slbuild('My_verify_tst');Вы также можете использовать uvmbuild функция для генерации UVM- испытательного стенда. Если ваша экспериментальная модель содержит verify операторы, они сопоставлены с утверждениями в вашем окружении UVM, и данные о покрытии собираются.

Измените текущую папку на dpi_tb папка, которая находится в папке генерации кода в вашем Симуляторе HDL установке. Запустите Симулятор HDL и сгенерированный скрипт, чтобы начать симуляцию. Выходы симуляции согласуются с выходами Simulink.

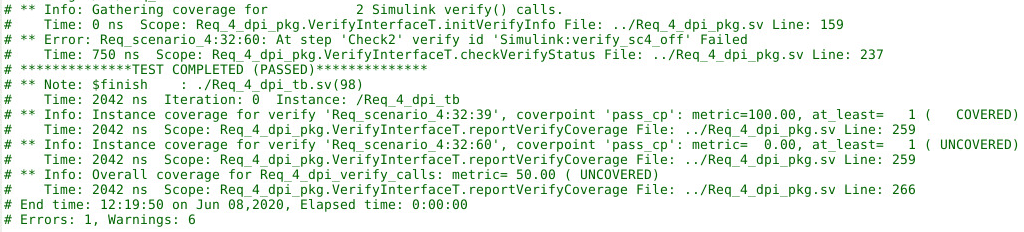

После завершения симуляции отображается информация о покрытии для каждого значения. По умолчанию утверждение считается покрытым, если оно оценивалось хотя бы один раз.

Дополнительные сведения о выполнении симуляции см. в разделе Проверка сгенерированного компонента на соответствие данным Simulink.

Каждая сгенерированная ошибка или предупреждение отображает уникальное имя, идентифицирующее ее источник. Этот номер является идентификатором Simulink (SID) этого блока. Для примера в этом журнале показана ошибка, сгенерированная блоком с SID Req_scenario_4:32:60.

# ** Error: Req_scenario_4:32:60: At step 'Check2' verify id 'Simulink:verify_sc4_off' Failed

У вас может быть несколько шагов в тестовой последовательности, которые используют verify оценка или несколько компонентов DPI, регистрирующих предупреждения из симуляции. В вашей экспериментальной модели можно фильтровать сгенерированный выход для определенных verify проверяет, задавая связанный SID как аргумент плюс в командной строке и приравнивая SID к -1. Для примера, чтобы выключить все выходы и функциональное покрытие для SID Req_scenario_4:32:60введите этот код в командной строке HDL.

vsim -c -sv_lib ../Req_4 work.Req_4_dpi_tb +Req_scenario_4:32:60=-1

Можно использовать блоки утверждений и verify операторы для сбора функционального покрытия во время симуляции SystemVerilog. После генерации SystemVerilog используя uvmbuild или slbuild (Simulink) функции, задайте цели покрытия для каждого утверждения. После завершения симуляции SystemVerilog просмотрите результаты в сгенерированном файле журнала или используйте сторонний инструмент для извлечения результатов. Цель покрытия по умолчанию является, по крайней мере, одним проходным выполнением утверждения или verify вызов.

Чтобы увеличить функциональную цель покрытия для определенного значения, укажите связанный SID как аргумент плюс в командной строке и приравняйте SID к вашей цели покрытия. Например, чтобы увеличить цель покрытия verify оператор с SID- Req_scenario_4:32:60 от одного до двух проходящих проверок по умолчанию введите этот код в командной строке HDL.

vsim -c -sv_lib ../Req_4 work.Req_4_dpi_tb +Req_scenario_4:32:60=2

По умолчанию сгенерированный компонент DPI выводит ошибку, когда функциональная точка покрытия оценивается и прекращает работать. Чтобы увидеть дополнительный выход, сгенерированный функциональной точкой покрытия, введите аргумент +VERBOSE_VERIFY в командной строке симуляции. Этот аргумент добавляет эту дополнительную информацию:

UNTESTED - Когда функциональная точка покрытия не была оценена

PASSED - Когда функциональная точка покрытия была оценена, и тест прошел

Для примера при использовании ModelSim®введите этот код в командной строке.

vsim -c -sv_lib ../Req_4 work.Req_4_dpi_tb +VERBOSE_VERIFY

После выполнения симуляции SystemVerilog с сгенерированной тестовой последовательностью в вашем файле журнала отображаются предупреждения и ошибки. Чтобы идентифицировать, какой блок вызвал конкретное предупреждение или выход ошибки, используйте hilite_system (Simulink) функция.

Например, чтобы выделить блок, который сгенерировал предупреждение для SID Req_scenario_4:32:60введите этот код в командной строке MATLAB.

hilite_system('Req_scenario_4:32:60');Этот рисунок подсвечивает оператор проверки и блок тестовой последовательности, который создал предупреждение.

Для получения дополнительной информации о SID смотрите Simulink Identifiers (Simulink).